# MATRIX FACTORIZATION USING A BLOCK-RECURSIVE STRUCTURE AND BLOCK-RECURSIVE ALGORITHMS

Jeremy D. Frens

Submitted to the faculty of the Graduate School

in partial fulfillment of the requirements

for the degree

Doctor of Philosophy

in the Department of Computer Science

Indiana University

August 2002

| Accepted by the Graduate     | Faculty, Indiana University, in partial ful- |

|------------------------------|----------------------------------------------|

| fillment of the requirements | s of the degree of Doctor of Philosophy.     |

|                              |                                              |

| Doctoral Committee           | David S. Wise (Principal Advisor)            |

|                              |                                              |

|                              | Randall Bramley                              |

|                              |                                              |

|                              | Dennis Gannon                                |

|                              |                                              |

| May 22, 2002                 | Daniel Maki                                  |

# Acknowledgements

This work was supported, in part, by the National Science Foundation under grant number CDA93-03189 and by the U.S. Department of Education under grant numbered P200A50237.

I first thank the members of my committee for helping me through this dissertation. Thanks especially to my advisor David S. Wise for all of his help and encouragement. Thanks to the other members of the committee, Randy Bramley, Dennis Gannon, and Daniel Maki, who had to stretch their memories to recall who I was when I started scheduling my defense. A special thanks to Randy who reminded me exactly what I needed to do.

For technical assistance, my thanks to Bruce Shei who helped me many times when I had problems with and questions about the various machines. Without Bruce, this dissertation wouldn't be here. Also, thanks to Greg Alexander who wrote a library for parallel dispatch system for quadtree matrices. I'm not sure what I would have done without that library.

Thanks also to all of my colleagues at both Northwestern College and Calvin College. Thanks for the support and encouragement that everyone from both institutions gave me.

My friends in Bloomington, Orange City, and Grand Rapids also deserve a lot of thanks. Those I knew in Bloomington: Dave Wilson for agreeing to room with me for three years; Kyle and Amy Wagner for their friendship and spaghetti nights; Peter Weingartner, Eric Hilsdale, and Susan Lato for their friendships and tollerance of lengthy discussions, usually about nothing; and all of my other friends at IU who aren't listed here. Those I knew in Orange City: Jeff and Jana Boersma who were familiar faces from a previous era; Mark Vellinga who was an excellent colleague; and all of the students I knew at Northwestern. And now those I knew and know in Grand Rapids, especially to Marie Albers who still remains a best friend after so many years. Also thanks to my Computer Science colleagues at Calvin; a special thanks to Joel Adams and David Laverell for proofreading my dissertation at the last minute.

Finally, my greatest thanks goes to my family. First to my family at United Presbyterian Church in Bloomington. You were my family for six years while I lived there, and I owe you more than I could ever repay. A special thanks to David Bremer who was a good cross between a brother and a father for me. Most importantly, I thank my biological family. Thanks to my Uncle Bud and Aunt Ruth who look after me now just as they did earlier. Thanks to my grandparents who have been supportive throughout my education. Thanks to sister Staci, brother Joel, and sister-in-law Rachel who befriended me while we were all at Calvin. And thanks to my parents who have done more for me than should be required of any parents; it was because of your encouragement and examples that got me here. This dissertation is for you, Mom and Dad.

# Abstract

The divide-and-conquer paradigm yields algorithms that parallelize easily, a very important consideration in high-performance computing. However, high-performance computing also relies on local reuse of data in a memory hierarchy of registers, caches, main memory, and swapping disks.

I have worked with a sequential representation of quadtree matrices that is a divide-and-conquer data structure. This representation uses an indexing scheme, Morton ordering, that automatically blocks the elements of the matrix and promotes memory locality in recursive algorithms over the quadtree. This work focuses on using this representation for two important matrix algorithms, matrix multiplication and QR factorization.

Techniques for generating independant and local code were discovered while implementing a recursive matrix-matrix multiplication over the sequential quadtree matrix. For good memory locality the basic multiplication routine was written as two dual, mutually recursive functions with the recursive calls in each version precisely ordered to reuse data already in cache.

To avoid unnessary work, minimal decorations annotate each submatrix of the matrix; these decorations are used to ignore zero blocks and to ellide the zero tests on

blocks known to be dense. Finally, a strategy was developed for dispatching parallel processes in the multiplication algorithm.

These lessons were then used to develop an efficient QR factorization algorithm for quadtree matrices. It also uses recursive functions that localize data in blocks and that balance parallel processing.

The sequential quadtree matrix and multiplication functions are implemented in C because of its optimizing compilers. Since C optimizers favor iterative code and are deficient for recursive code, some base optimizations were done by hand. These hand optimizations could and should be done by some future optimizing compiler.

Results are mostly favorable; while the quadtree-matrix algorithms do not always perform at the same level as decades-old routines (i.e., BLAS and LAPACK), which are fine-tuned for traditional storage, the quadtree algorithms are competitive and even expose some flaws in these old routines.

# Contents

| A | ckno  | wledge  | ements                             | iii     |

|---|-------|---------|------------------------------------|---------|

| A | bstra | ct      |                                    | ${f v}$ |

| 1 | Intr  | oduct   | ion                                | 1       |

|   | 1.1   | Divide  | e-and-Conquer Paradigm for         |         |

|   |       | High-l  | Performance Computing              | 1       |

|   | 1.2   | Parall  | elism                              | 2       |

|   |       | 1.2.1   | Divide-and-Conquer Algorithms      | 2       |

|   |       | 1.2.2   | Divide-and-Conquer Parallelism     | 4       |

|   | 1.3   | Efficie | nt Memory Use                      | 5       |

|   |       | 1.3.1   | Divide-and-Conquer Data Structures | 5       |

|   |       | 1.3.2   | The Memory Hierarchy               | 6       |

|   | 1.4   | Proble  | ems in High-Performance Computing  | 9       |

|   |       | 1.4.1   | Matrix Terminology                 | 9       |

|      | 1.4.2   | Matrix Multiplication               | 12  |

|------|---------|-------------------------------------|-----|

|      | 1.4.3   | Solving a Linear System             | 12  |

|      | 1.4.4   | Problems with Matrix Algorithms     | 13  |

| 1.5  | Tradit  | ional Matrix Storage                | 14  |

| 1.6  | The Q   | uadtree Matrix                      | 15  |

|      | 1.6.1   | Trees                               | 15  |

|      | 1.6.2   | Quadtree Indexings                  | 17  |

|      | 1.6.3   | Quadtree Matrix                     | 19  |

|      | 1.6.4   | Quadtree Matrix Implementation      | 22  |

|      | 1.6.5   | Decorating Quadtree Matrices        | 24  |

|      | 1.6.6   | Storage Arrays                      | 25  |

|      | 1.6.7   | A Divide-and-Conquer Data Structure | 27  |

| 1.7  | Row N   | Major Versus Morton Order           | 28  |

| 1.8  | Relate  | d Research                          | 29  |

| 1.9  | New C   | Contributions                       | 31  |

| 1.10 | Road    | Map                                 | 32  |

| Hig  | h-Perfe | ormance Environment                 | 33  |

| 2.1  |         | of Concept                          | 33  |

|      |         | amming Liberties                    | 3/1 |

2

|   | 2.3 | Machi  | nes                                      | 35 |

|---|-----|--------|------------------------------------------|----|

|   | 2.4 | Comp   | iler Issues                              | 35 |

|   |     | 2.4.1  | Compilers and Libraries                  | 35 |

|   |     | 2.4.2  | Stride                                   | 37 |

|   |     | 2.4.3  | Recursive Code                           | 37 |

|   |     | 2.4.4  | Compiler Flags                           | 38 |

|   |     | 2.4.5  | Shared Memory and Parallel Dispatch      | 38 |

|   | 2.5 | Timin  | g Issues                                 | 40 |

|   |     | 2.5.1  | Measuring Performance                    | 40 |

|   |     | 2.5.2  | Machine Solutions                        | 41 |

| 3 | Mat | trix M | ultiplication                            | 42 |

|   | 3.1 | Row-N  | Major Multiplication                     | 42 |

|   | 3.2 | Quadt  | ree Matrices                             | 44 |

|   |     | 3.2.1  | Two Versions of Matrix Multiplication    | 44 |

|   |     | 3.2.2  | Analytical Proof of Good Memory Behavior | 46 |

|   | 3.3 | Succes | ssful Matrix Multiplication              | 49 |

|   | 3.4 | Comp   | iler and Implementation Issues           | 50 |

|   |     | 3.4.1  | BLAS                                     | 50 |

|   |     | 3.4.2  | Unfolding the Base Case                  | 50 |

|   |     | 3.4.3   | Decoration Driven Multiplication         | 52 |

|---|-----|---------|------------------------------------------|----|

|   |     | 3.4.4   | Destructive Multiplication               | 53 |

|   |     | 3.4.5   | Decorating $C$                           | 55 |

|   |     | 3.4.6   | Top Level Function                       | 56 |

|   | 3.5 | Exper   | imental Results                          | 56 |

|   |     | 3.5.1   | Base Case Size                           | 57 |

|   |     | 3.5.2   | Flop Counts                              | 58 |

|   |     | 3.5.3   | Quadtree Algorithm Versus BLAS Algorithm | 58 |

| 4 | Par | allel M | Iatrix Multiplication                    | 65 |

|   | 4.1 | Dispat  | tching Parallel Processes                | 65 |

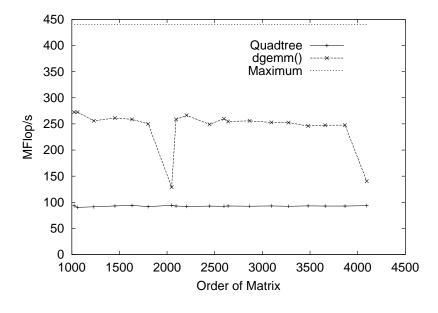

|   | 4.2 | Eight   | Multiplication Patterns                  | 66 |

|   | 4.3 | Implei  | mentation and Compiler Issues            | 75 |

|   |     | 4.3.1   | Padding Size                             | 76 |

|   |     | 4.3.2   | Uniprocessor-Commit Size                 | 76 |

|   | 4.4 | Exper   | imental Results                          | 77 |

| 5 | QR  | Factor  | rization                                 | 81 |

|   | 5.1 | The B   | asic Algorithms                          | 81 |

|   |     | 5.1.1   | Householder $QR$ Factorization           | 82 |

|   |     | 5.1.2   | Givens $QR$ Factorization                | 82 |

| 5.2 | The C  | Quadtree $QR$ Factorization Algorithms     | 84 |

|-----|--------|--------------------------------------------|----|

|     | 5.2.1  | Quadtree $QR$ Factorize                    | 84 |

|     | 5.2.2  | Quadtree $QR$ Eliminate                    | 84 |

| 5.3 | Tunin  | g for the Memory Hierarchy                 | 86 |

| 5.4 | Succes | ssful $QR$ Factorization                   | 88 |

|     | 5.4.1  | Computational Correctness                  | 88 |

|     | 5.4.2  | Avoiding Problematic Operations            | 89 |

|     | 5.4.3  | Error Analysis                             | 90 |

| 5.5 | Imple  | mentation and Compiler Issues              | 90 |

|     | 5.5.1  | In-place Algorithms                        | 90 |

|     | 5.5.2  | The Transpose of $Q$                       | 91 |

|     | 5.5.3  | Base Case Unfolding                        | 91 |

|     | 5.5.4  | Decoration Driven $QR$ Factorization       | 91 |

|     | 5.5.5  | Accumulating $Q$                           | 92 |

| 5.6 | LAPA   | CK                                         | 92 |

| 5.7 | Exper  | imental Results                            | 93 |

|     | 5.7.1  | Flop Count                                 | 93 |

|     | 5.7.2  | Quadtree Algorithm Versus LAPACK Algorithm | 94 |

| 6 | Par | allel $QR$ Factorization            | 102 |

|---|-----|-------------------------------------|-----|

|   | 6.1 | QR Parallel Cases                   | 102 |

|   |     | 6.1.1 Parallel Patterns of $f$      | 103 |

|   |     | 6.1.2 Parallel Patterns of $e$      | 104 |

|   | 6.2 | Parallel LAPACK                     | 110 |

|   | 6.3 | Experimental Results                | 110 |

| 7 | Con | nclusion                            | 115 |

|   | 7.1 | Results                             | 115 |

|   | 7.2 | Comments                            | 116 |

|   | 7.3 | Future Work                         | 117 |

|   |     | 7.3.1 Rectangular Matrices          | 117 |

|   |     | 7.3.2 Processor Dispatch            | 118 |

|   |     | 7.3.3 Concise Representation of $Q$ | 119 |

|   |     | 7.3.4 Sparse Matrices               | 119 |

|   |     | 7.3.5 Other Algorithms              | 120 |

|   |     | 7.3.6 Patterns in Algorithms        | 121 |

|   | 7.4 | Curious Observations                | 121 |

|   | 75  | Conclusion                          | 199 |

| A                    | Pro   | ofs                               | 125 |

|----------------------|-------|-----------------------------------|-----|

|                      | A.1   | Transpose Properties              | 125 |

|                      | A.2   | Lemmas for Orthogonal Matrices    | 126 |

|                      | A.3   | Correctness of $QR$ Factorization | 129 |

|                      | A.4   | QR Factorization Success          | 142 |

| $\mathbf{R}\epsilon$ | efere | aces                              | 144 |

# List of Tables

| 1.1 | Matrix notation                                | 10 |

|-----|------------------------------------------------|----|

| 1.2 | Correlation of quadrants to index computations | 22 |

| 2.1 | System parameters of Power Challenge           | 35 |

| 2.2 | System parameters of Octane                    | 36 |

| 2.3 | System parameters of Enterprise 450            | 36 |

| 2.4 | System parameters of Ultra 5/10                | 37 |

| 2.5 | Compiler optimizations for SGIs                | 39 |

| 2.6 | Compiler optimizations for Suns                | 39 |

# List of Figures

| 1.1  | Factorial function (Version A)                                 | 3  |

|------|----------------------------------------------------------------|----|

| 1.2  | Factorial function (Version B)                                 | 3  |

| 1.3  | Quicksort function                                             | 3  |

| 1.4  | Row-major indexing                                             | 15 |

| 1.5  | Column-major indexing                                          | 15 |

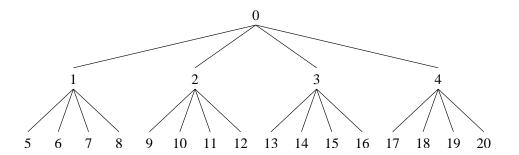

| 1.6  | Level-order indexing of quaternary tree                        | 17 |

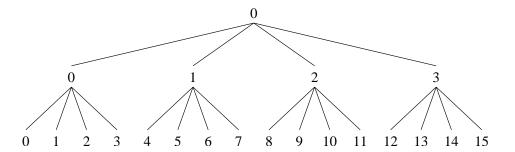

| 1.7  | Morton-order indexing of quaternary tree                       | 18 |

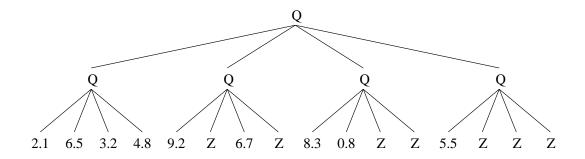

| 1.8  | Matrix $M_1$                                                   | 19 |

| 1.9  | Matrix $M_1$ padded                                            | 19 |

| 1.10 | Quadtree matrix representation of $pad(M_1)$                   | 19 |

| 1.11 | Matrix $M_2$                                                   | 20 |

| 1.12 | Matrix $M_2$ padded                                            | 20 |

| 1.13 | Quadtree matrix representation of $pad(M_2)$ $\downarrow$ $ne$ | 20 |

| 1.14 | Morton ordering of a 16 $\times$ 16 matrix with Z order        | 23 |

| 1.15 | Level-order storage of pad $(M_1)$ decoration (cf. Figure 1.9)                              | 20 |

|------|---------------------------------------------------------------------------------------------|----|

| 1.16 | Morton-order storage of $pad(M_1)$ scalars                                                  | 26 |

| 1.17 | Level-order storage of $\operatorname{pad}(M_2 \downarrow ne)$ decoration (cf. Figure 1.12) | 27 |

| 1.18 | Morton-order storage of $pad(M_2 \downarrow ne)$ scalars                                    | 27 |

| 3.1  | Nested loops for inner-product multiplication                                               | 42 |

| 3.2  | Blocked nested loops for multiplication                                                     | 43 |

| 3.3  | Cache-poor quadtree matrix multiplication                                                   | 45 |

| 3.4  | Cache-friendly quadtree multiplication                                                      | 46 |

| 3.5  | Original unfolded $2 \times 2$ base case                                                    | 51 |

| 3.6  | Rolled $2 \times 2$ base case                                                               | 51 |

| 3.7  | Raised base case version of multiplication                                                  | 53 |

| 3.8  | First-visit version of multiplication                                                       | 54 |

| 3.9  | Last-visit version of multiplication                                                        | 55 |

| 3.10 | Top-level multiplication function                                                           | 56 |

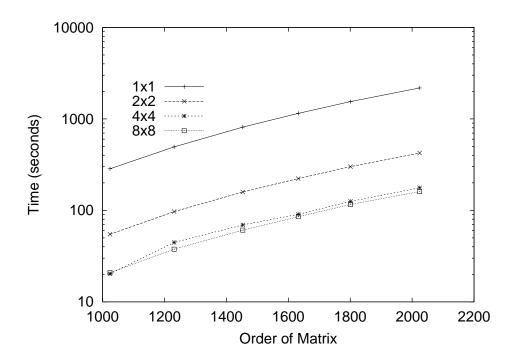

| 3.11 | Running time of different base case sizes                                                   | 57 |

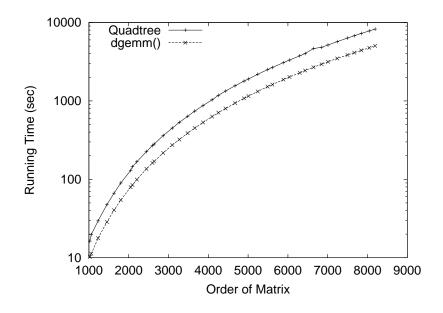

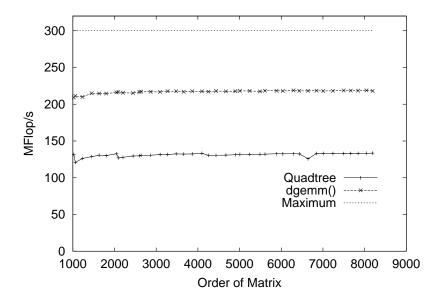

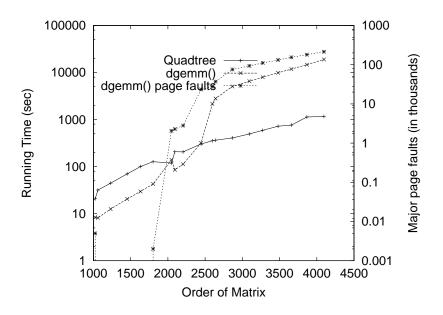

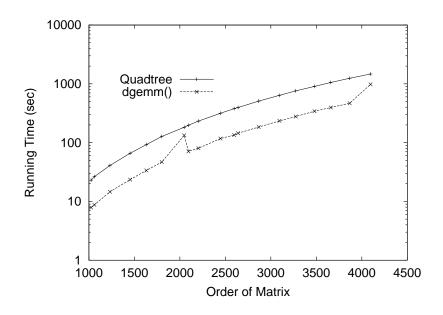

| 3.12 | Running time of uniprocessor multiplication on Power Challenge                              | 61 |

| 3.13 | Mflop/s of uniprocessor multiplication on Power Challenge                                   | 61 |

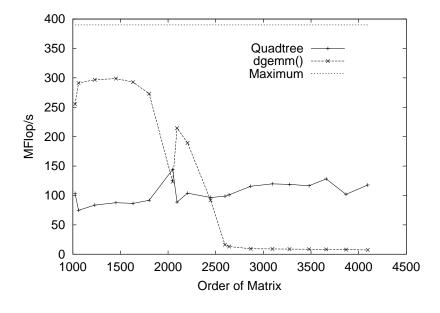

| 3.14 | Running time of uniprocessor multiplication on Octane                                       | 62 |

| 3.15 | Mflop/s of uniprocessor multiplication on Octane                                            | 62 |

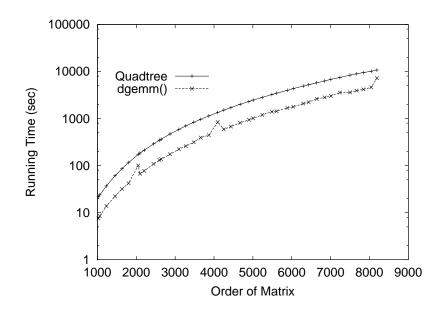

| 3.16 | Running time of uniprocessor multiplication on Enterprise 450                          | 63 |

|------|----------------------------------------------------------------------------------------|----|

| 3.17 | Mflop/s of uniprocessor multiplication on Enterprise 450                               | 63 |

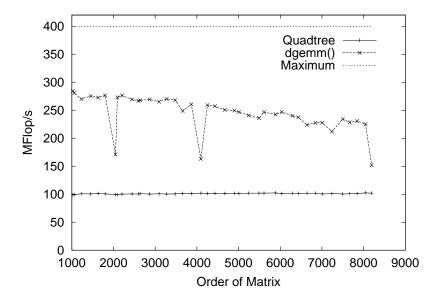

| 3.18 | Running time of uniprocessor multiplication on Ultra $5/10$                            | 64 |

| 3.19 | Mflop/s of uniprocessor multiplication on Ultra 5/10                                   | 64 |

| 4.1  | Parallel multiplication patterns                                                       | 67 |

| 4.2  | Parallel dispatch chart                                                                | 67 |

| 4.3  | Parallel multiplication: perfect square dispatch                                       | 70 |

| 4.4  | Parallel multiplication: perfect square dispatch (4 processes)                         | 70 |

| 4.5  | Parallel multiplication: square osquare dispatch                                       | 70 |

| 4.6  | Parallel multiplication: square $\bullet$ colonnade majority-padding dispatch .        | 72 |

| 4.7  | Parallel multiplication: square $\bullet$ colonnade minority-padding dispatch .        | 72 |

| 4.8  | Parallel multiplication: stripe $\bullet$ square majority-padding dispatch             | 72 |

| 4.9  | Parallel multiplication: stripe $\bullet$ square minority-padding dispatch             | 72 |

| 4.10 | $Parallel\ multiplication:\ colonnade \bullet square\ majority-padding\ dispatch\ .$   | 74 |

| 4.11 | $Parallel\ multiplication:\ colonnade \bullet square\ minority-padding\ dispatch\ .$   | 74 |

| 4.12 | Parallel multiplication: square•stripe majority-padding dispatch                       | 74 |

| 4.13 | Parallel multiplication: square•stripe minority-padding dispatch                       | 74 |

| 4.14 | $Parallel\ multiplication:\ colonnade \bullet stripe\ majority-padding\ dispatch\ \ .$ | 74 |

| 4.15 | Parallel multiplication: colonnade•stripe minority-padding dispatch .                  | 74 |

| 4.16 | Parallel multiplication: stripe $\bullet$ colonnade majority-padding dispatch . | 75  |

|------|---------------------------------------------------------------------------------|-----|

| 4.17 | Parallel multiplication: stripe $\bullet$ colonnade minority-padding dispatch . | 75  |

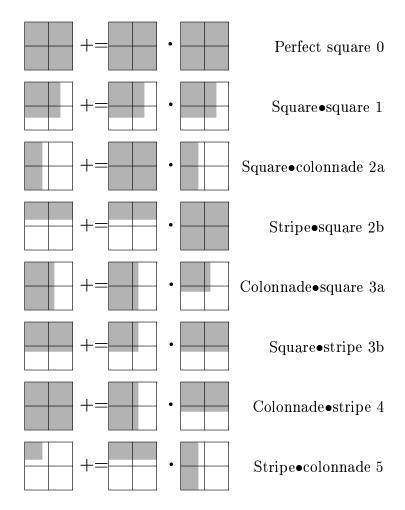

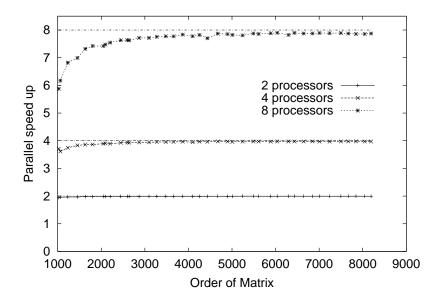

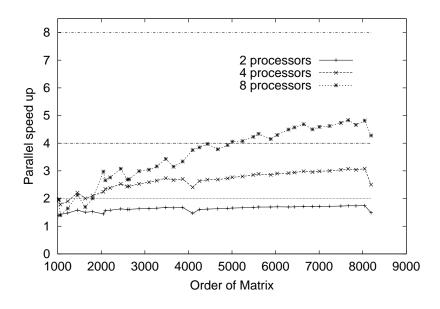

| 4.18 | Speed-up for quadtree multiplication on Power Challenge                         | 79  |

| 4.19 | Speed-up for dgemm() on Power Challenge                                         | 79  |

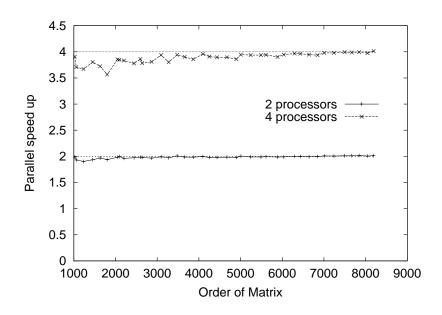

| 4.20 | Speed-up for quadtree multiplication on Enterprise 450                          | 80  |

| 4.21 | Speed-up for dgemm() on Enterprise 450                                          | 80  |

| 5.1  | Iterative, column-based $QR$ factorization using Givens rotations               | 83  |

| 5.2  | QR factorization function, $f$                                                  | 85  |

| 5.3  | QR elimination function, $e$                                                    | 87  |

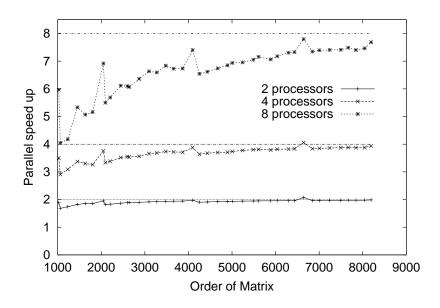

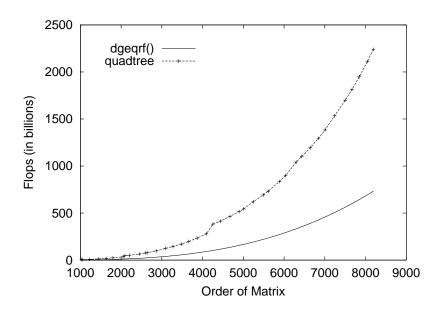

| 5.4  | Flop count of $QR$ factorization algorithms                                     | 93  |

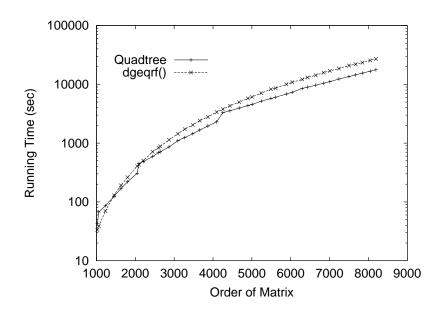

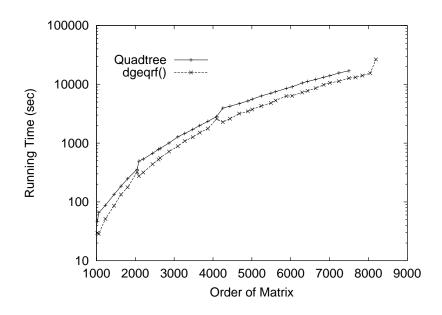

| 5.5  | Running time of uniprocessor $QR$ factorization on Power Challenge $\ .$        | 98  |

| 5.6  | Mflop/s of uniprocessor $QR$ factorization on Power Challenge                   | 98  |

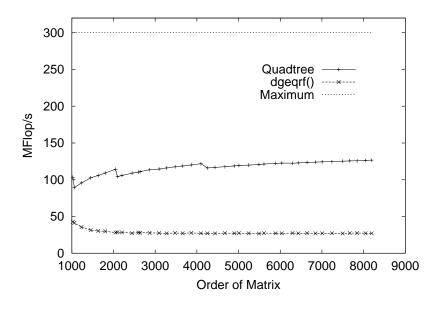

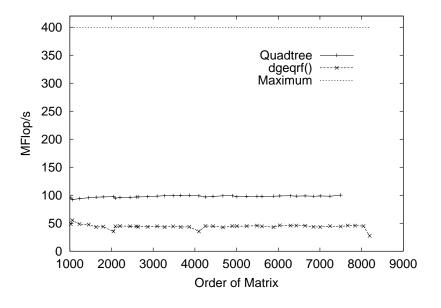

| 5.7  | Running time of uniprocessor $QR$ factorization on Octane $\dots$               | 99  |

| 5.8  | Mflop/s of uniprocessor $QR$ factorization on Octane                            | 99  |

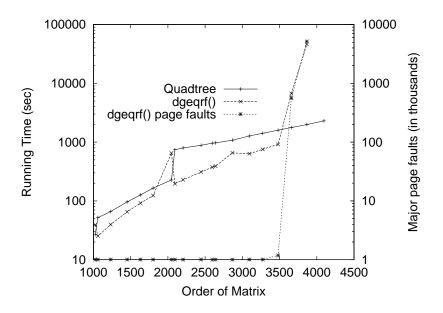

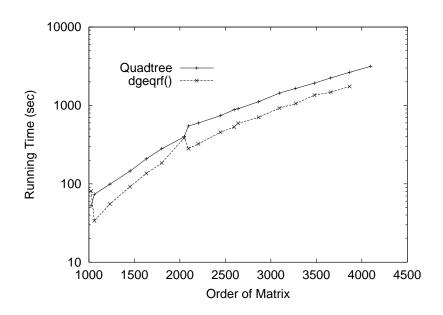

| 5.9  | Running time of uniprocessor $QR$ factorization on Enterprise 450 $$            | 100 |

| 5.10 | Mflop/s of uniprocessor $QR$ factorization on Enterprise 450                    | 100 |

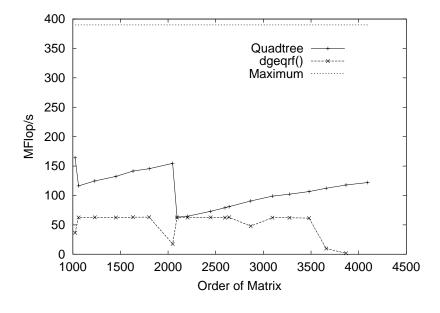

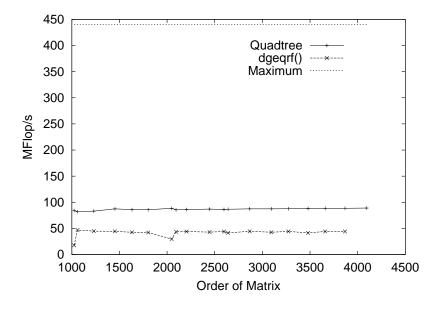

| 5.11 | Running time of uniprocessor $QR$ factorization on Ultra $5/10$                 | 101 |

| 5.12 | Mflop/s of uniprocessor $QR$ factorization on Ultra $5/10$                      | 101 |

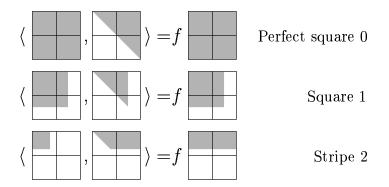

| 6.1  | Parallel patterns of $f$                                                        | 103 |

| 6.2  | Parallel $QR$ factorization: perfect square dispatch                | 105 |

|------|---------------------------------------------------------------------|-----|

| 6.3  | Parallel $QR$ factorization: square and stripe dispatch             | 105 |

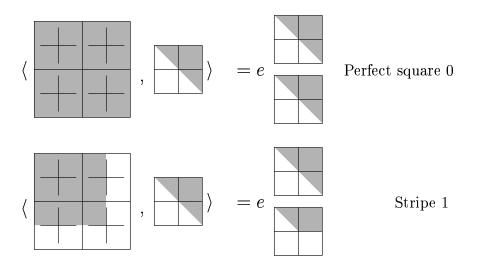

| 6.4  | Parallel patterns of $e$                                            | 106 |

| 6.5  | Parallel $QR$ elimination: perfect square dispatch                  | 107 |

| 6.6  | Parallel $QR$ elimination: stripe majority-padding dispatch         | 108 |

| 6.7  | Parallel $QR$ elimination: stripe minority-padding dispatch         | 109 |

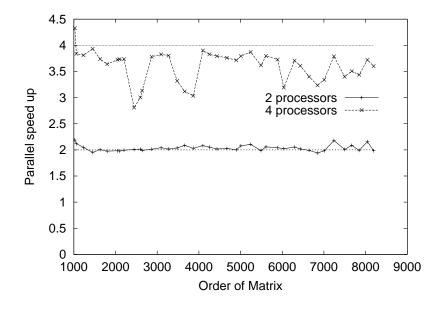

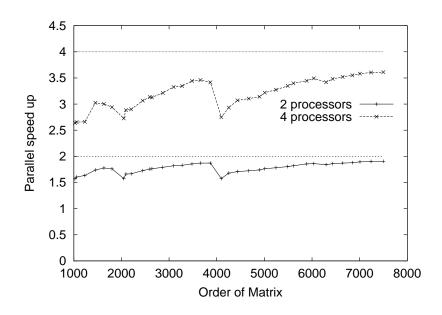

| 6.8  | Speed-up for quadtree $QR$ factorization on Power Challenge $\dots$ | 113 |

| 6.9  | Speed-up for quadtree $QR$ factorization on Enterprise 450 $\dots$  | 114 |

| 6.10 | Speed-up for dgeqrf() on Enterprise 450                             | 114 |

| 7 1  | Modified parallel <i>QR</i> elimination (perfect square) dispatch   | 122 |

# Introduction

# 1.1 Divide-and-Conquer Paradigm for High-Performance Computing

This dissertation addresses the divide-and-conquer paradigm in the context of high-performance computing, where data sets are huge and algorithms take a long time to run. High-performance computing has two main concerns for efficient programs. The first concern is parallelism [50] which has long been a promise of the divide-and-conquer paradigm: compute all independent expressions in parallel [13, Section 1.3.1][3]. The second concern of high-performance computing is the reuse of a computer's memory [37, Chapter 7], respecting the different types of memory in a computer and programming accordingly. This concern also has a divide-and-conquer solution.

Divide-and-conquer is a common tool in algorithm design, but crucial to functional programming [8] which motivated this research. Functional programming is a

paradigm where computations are expressed using only functions and arguments, excluding side-effects and hence unnecessary sequentiality; so syntactically independent subexpressions are computationally independent as well. The divide-and-conquer paradigm splits a problem into a few *independent* and *local* subproblems.

## 1.2 Parallelism

The divide-and-conquer paradigm has long promised and delivered good parallelism. A couple of classic examples demonstrate how.

#### 1.2.1 Divide-and-Conquer Algorithms

A divide-and-conquer algorithm divides a problem into multiple subproblems, and often the subproblems can be solved independently of each other. Solutions for the subproblems are later combined together to yield a solution for the original problem.

The canonical example of functional programming is the factorial function as written in Figure 1.1 [13, p. 6] using Haskell [8]. However, this formulation does not use divide-and-conquer since there is only one function call (i.e., one subproblem) in the recursive case. Divide-and-conquer is used in the second version of the factorial function in Figure 1.2 [13, p. 6] through the use of a second function prod. The function prod multiplies a sequence of consecutive integers by splitting the sequence in two and calling itself recursively on each half.

The divide-and-conquer paradigm can also be used for sorting elements in a list. Quicksort [27] is one such algorithm, presented in Figure 1.3 [38, p. 119] also using

```

facA 0 = 1

facA n = n * facA (n-1)

Figure 1.1: Factorial function (Version A)

facB 0 = 1

facB n = prod 1 n

prod n m = if m=n then m

else (prod m halfway) * (prod halfway+1 n)

where halfway = m + ((n-m) div 2)

Figure 1.2: Factorial function (Version B)

qsort [] = []

qsort (pivot:rest) = qsort lower ++ [pivot] ++ qsort upper

where lower = [ x | x <- rest, x <= pivot]

upper = [ x | x <- rest, x > pivot]

```

Figure 1.3: Quicksort function

Haskell. The inductive case for the qsort function receives a list as indicated by the colon operator<sup>1</sup>: the first element of the list is called pivot, and the rest of the list is aptly named rest. The rest of the list is partitioned into two separate lists, upper and lower, by "pivoting" around pivot using two list comprehensions<sup>2</sup>. The list lower will contain elements less than or equal to the pivot; the list upper will contain elements greater than the pivot. Both of these lists are sorted recursively and then concatenated into a result with the infix list-concatenation operator ++.

<sup>&</sup>lt;sup>1</sup>The colon operator is the infix cons operator; Haskell allows the operator to be used in the pattern matching of parameters. [8, Section 4.1.1]

<sup>&</sup>lt;sup>2</sup>Read list comprehensions as set notation with the vertical bar | meaning "such that" and the left arrow operator <- meaning "element of". [8, Section 4.3.2]

#### 1.2.2 Divide-and-Conquer Parallelism

An essential step in writing parallel algorithms is partitioning computations into processes that can be executed in parallel. The divide-and-conquer paradigm offers a straightforward way of writing parallel code: take the divide-and-conquer algorithm and solve independent subproblems in parallel.

For example, the two recursive calls in prod in Figure 1.2 might be done in parallel. The quicksort algorithm of Figure 1.3 has two opportunities for parallelism:

(1) computing upper and lower, and (2) the two recursive calls to qsort.

Scheduling the processes is complicated by several factors. One factor is interprocess communication [1, 14, 28] which must be minimized. When the divide-and-conquer paradigm schedules independent computations in parallel, there is no interprocess communication while these processes execute. Inter-process communication is needed only as parallel processes are dispatched and after they end. Consequently, the number of dispatches should be minimized, and this is accomplished by dispatching parallel processes early in the recursive decomposition.

Even more importantly, all of the available processors must be kept busy with useful work. One simple solution is to dispatch parallel processes that are given the same amount of work as each other; each process is given an equal number of processors for further dispatch. The function prod (Figure 1.2) balances its parallel processes quite well: each process is given half of the sequence to multiply together. Each process would be given half of the available processors for further dispatch.

Some algorithms are not as elegant. For example, balancing the parallel processes of quicksort (Figure 1.3) cannot use the same elegant solution as prod. The two list

comprehensions can be done in parallel; both list comprehensions take about the same amount of work (i.e., both process the whole original list) resulting in well balanced processes. However, depending on the pivot element, the lengths of upper and lower may be quite different from each other, resulting in significantly different amounts of work to sort each one individually. For these parallel processes, each process could be given a number of processors proportional to the length of the list given to that process.

## 1.3 Efficient Memory Use

The divide-and-conquer paradigm has long been used to design a variety of abstract data structures. However, often in functional programming, the implementations of these data structures have been done using linked structures. Linked structures tend to suffer in performance in high-performance computing because of data locality problems, so other solutions must be used. The divide-and-conquer paradigm offers one solution.

# 1.3.1 Divide-and-Conquer Data Structures

Divide-and-conquer can be applied in at least two ways for a data structure.

First, the divide-and-conquer paradigm can be used in the design of the abstract data structure. Trees are the most common divide-and-conquer data structures. (See

Section 1.6.1 for a more formal discussion of trees.) Binary search trees [30, Section 6.2.2] and multi-way trees like B-trees [30, Section 6.2.4] are dictionary structures that partition the data, one partition for each subtree. The partitioning is done deliberately so that common operations like insert and search are very efficient, proportional to the height of the tree.

Divide-and-conquer algorithms arise naturally from exploiting the substructures of a divide-and-conquer data structure. Tree traversals [29, Section 2.3.1] can be divide-and-conquer algorithms.

Second, the divide-and-conquer paradigm can also be applied to the manifestation of a data structure; that is, it can be used to determine how to map the abstract data structure directly into a computer's memory. Row-major storage of a matrix (see Section 1.5) follows this approach: divide the matrix into rows, and map each element of each row into consecutive locations in memory. The sequential storage of the heap used in heapsort [30, p. 144] also follows this approach: store the levels of the heap (a tree) in consecutive location in memory.

## 1.3.2 The Memory Hierarchy

The memory of a modern computer is layered in a hierarchy, top to bottom<sup>3</sup>: primary cache, secondary cache, main memory, virtual memory, and distributed memory—with more levels to come in the future.

**Definition 1.1** The transfer block of a level of the memory hierarchy is the smallest

<sup>&</sup>lt;sup>3</sup>This dissertation follows the tradition that memories closer to the processor are higher in the hierarchy (see Patterson and Hennessy [37, p. 542]); this is by no means universal (see Whaley and Dongarra [45]).

block of contiguous memory uploaded to that level of the memory hierarchy.

This is a generalization of familiar concepts: a cache line is the transfer block of a cache; a page of virtual memory is the transfer block of a virtual memory system into main memory. Patterson and Hennessy [37, p. 542] use the term "block" for this same concept.

**Definition 1.2** A memory miss is a memory access that triggers the transfer of a transfer block into a level of the memory hierarchy.

This, too, is a generalization of familiar concepts: a cache miss is a memory miss in a cache; a page fault is a memory miss in virtual memory. Again, see Patterson and Hennessy [37, p. 542].

The different types of memory in the hierarchy have different relative speeds and sizes. The top of the hierarchy is very fast; the bottom of the hierarchy is very slow. The size of transfer blocks tend to be small at the top and large on the bottom. The memories themselves are similarly small at the top and large on the bottom.

The large problems of high-performance computing and the cost of faster memories force the use of the slower memories lower in the hierarchy, and efficiency demands that algorithms minimize the number of times that the slower memories are accessed. As memory speeds fall further and further behind processor speeds [49], this demand becomes more and more important.

The number of memory misses can be reduced by increasing data locality. The memory hierarchy is managed with two types of locality in mind, temporal and spatial. *Temporal locality* suggests that once a data item is used, it will be used again soon.

Spatial locality suggests that if a program accesses one memory location, it will also access nearby memory locations. (See Patterson and Hennesy [37, p. 540].) Spatial locality explains why transfer blocks are blocks of contiguous memory. Temporal locality in turn suggests a programming style: when a memory location is accessed, use it and nearby data as much as possible, where "nearby" is defined by the transfer blocks of each level of the memory hierarchy.

Traditional analysis of algorithms ignores memory accesses by focusing on computational operations and assuming all accesses are done in constant time. Due to the variety of access times at different levels of the memory hierarchy, this assumption results in a misleading analysis. A more realistic analysis would account for the inevitable memory misses and the amount of time needed to access different memories. Asymptotically, this careful analysis is the same as the naive analysis; the difference is only apparent on the coefficients of the formulas for the analyses. Yet, often these coefficients are extremely significant. (After all, parallel speed-up is usually just a modification of the coefficient of the analysis.)

Programming with traditional storage requires an expert programmer or an optimizing compiler to respect the transfer blocks of the memory hierarchy. Often the sizes of these transfer blocks are used by this expert programmer, making the code unportable. This knowledge can be non-trivial since different computers have different types of memories with different sizes. It is better to have the compiler deal with this knowledge since it should be relatively easy for it to collect. Furthermore, since each type of computer can be configured with differently sized memories (especially RAM and virtual memory), the code should be compiled for each physical machine.

The divide-and-conquer paradigm offers a solution to all of these problems. Too often functional programming has ignored data locality, favoring linked structures whose components are scattered throughout memory. This oversight causes problems for computation-intense algorithms since the links may routinely cross transfer blocks causing many memory misses. But the divide-and-conquer paradigm applied to sequential storage offers a solution: map a data structure into memory by allocating blocks of contiguous memory for the substructures of a data structure. Memory can be allocated this way recursively down to the base case of the data structure so that every substructure at every level of the data structure is mapped into contiguous memory. A program then takes advantage of data locality simply by manipulating the substructures without knowledge of the machine's parameters.

# 1.4 Problems in High-Performance Computing

Typical problems in high-performance computing involve matrices. These problems are prime candidates for demonstrating how effective the divide-and-conquer paradigm can be for high-performance computing.

### 1.4.1 Matrix Terminology

Informally, a matrix is a two-dimensional grid of real numbers represented in the computer as floating point values [24, Section 2.4]. For example, if A is an  $m \times n$

| Symbol                  | Definition                                                                      |  |  |  |

|-------------------------|---------------------------------------------------------------------------------|--|--|--|

| $a_{ij}$                | Element of matrix $A$ in row $i$ , column $j$                                   |  |  |  |

| $A^{\alpha\beta} = A^T$ | Block in stripe $\alpha$ , colonnade $\beta$ in matrix $A$ (see Definition 1.9) |  |  |  |

| $A^T$                   | the transpose of $A$                                                            |  |  |  |

| $A^{-1}$                | the inverse of $A$                                                              |  |  |  |

| I                       | the identity matrix                                                             |  |  |  |

| Z                       | the zero matrix                                                                 |  |  |  |

| $A \downarrow dd$       | quadrant $dd$ of matrix $A$ where $dd$ can be $nw$ , $ne$ , $sw$ , or $se$ .    |  |  |  |

Standard matrix notation taken from Golub and Van Loan [24].

Table 1.1: Matrix notation

matrix (i.e., m rows and n columns), its grid would look like this:

$$A = \begin{bmatrix} a_{11} & a_{12} & \dots & a_{1n} \\ a_{21} & a_{22} & \dots & a_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ a_{m1} & a_{m2} & \dots & a_{mn} \end{bmatrix}$$

See Table 1.1 for the notation used for matrices.

Several basic terms are useful when talking about matrices:

**Definition 1.3** The transpose  $A^T$  of an  $m \times n$  matrix A is the  $n \times m$  matrix obtained from A by interchanging the rows with the columns; that is,  $a_{ij}^T = a_{ji}$ . [21, p. 15]

One of the most common matrix operations is matrix multiplication:

**Definition 1.4** Matrix-matrix multiplication is written C = AB, where A is an

$m \times p$  matrix, B is an  $p \times n$  matrix, and C is an  $m \times n$  matrix; it is defined by

$$c_{ij} = \sum_{k=1}^{p} a_{ik} b_{kj}, \tag{1.1}$$

for all  $1 \le i \le m$  and  $1 \le j \le n$ . [24, Section 1.1.2]

**Definition 1.5** The elements of the identity matrix I are all zero except for the elements on the main diagonal (where the row and column indices are equal) which are set to 1. (See Friedberg et al. [21, p. 75].)

The identity matrix is the multiplicative identity; for a square matrix, AI = IA = A.

**Definition 1.6** If A and X are  $n \times n$  matrices and satisfy AX = I, then X is the inverse of A and is denoted by  $A^{-1}$ . If  $A^{-1}$  exists, then A is said to be nonsingular. Otherwise, A is singular. [24, p. 50]

**Definition 1.7** A square matrix Q is said to be orthogonal if  $Q^TQ = I$ . [24, p. 69]

With this definition and some algebra, it can be proved that the transpose of an orthogonal matrix is its own inverse. Since its transpose is well-defined, an orthogonal matrix is always nonsingular.

Some matrices have particular shapes:

**Definition 1.8** An  $n \times n$  matrix A is upper triangular if  $a_{ij} = 0$  for all i > j. (See Golub and Van Loan [24, Section 1.2.1].)

Finally, adjacent rows or columns of a matrix can be conceptually combined together in groups: **Definition 1.9** A stripe is a set of adjacent rows in a matrix. A colonnade is a set of adjacent columns. [46, p. 33]

#### 1.4.2 Matrix Multiplication

Matrix multiplication (Definition 1.4) is one of the most common operations on matrices, often used as a kernel operation for other algorithms. Multiplication can be generalized to blocks of the matrices. For the simplification of notation, let A, B, and C be  $N \times N$  block matrices with  $\ell \times \ell$  blocks. Then

$$C_{\alpha\beta} = \sum_{\gamma=1}^{N} A_{\alpha\gamma} B_{\gamma\beta} \tag{1.2}$$

for all  $1 \leq \alpha \leq N$  and  $1 \leq \beta \leq N$  [24, Section 1.3.5]. Instead of multiplying individual rows and columns, a block of C is computed by multiplying a stripe of A with a colonnade of B. The blocks of these matrices are square only because the notation is simpler; the matrices and their blocks could be rectangular.

This definition does not specify how  $A_{\alpha\gamma}B_{\gamma\beta}$  should be multiplied. Equation 1.1 or Equation 1.2 is possible; the choice is the programmer's.

### 1.4.3 Solving a Linear System

A system of linear equations is commonly expressed in matrix form: given matrix A and vector b, one must solve Ax = b for vector x. When A is a square, nonsingular matrix, the solution is unique and determinable.

The direct approach for solving Ax = b is to factor A into other matrices that are

easily manipulated for finding x. For example, LU factorization factors A into two matrices L and U such that A = LU where L is unit lower triangular and U is upper triangular [24, Section 3.2]. Solving Ax = b for x then reduces to solving LUx = b. First, one solves Ly = b for y by a process called forward substitution; then Ux = y is solved for x by a process called backwards substitution [24, Section 3.1].

However, if A has more rows than columns, the system is said to be overdetermined; the problem is then framed in terms of finding an x such that the magnitude of the vector Ax - b is minimized. This is the least squares problem [24, Section 5.3].

A common factorization for solving the least squares problem is QR factorization [24, Section 5.2]. QR factorization factors A into Q and R such that A = QR where Q is orthogonal and R is upper triangular. The QR factorization can also be used to solve Ax = b for x; one computes  $y = Q^Tb$  (since Q is orthogonal) and then uses backwards substitution to solve Rx = y for x.

Another use for the QR factorization is as a fundamental operation in the QR Algorithm [24, Chapter 7] to find the eigenvalues of a matrix.

### 1.4.4 Problems with Matrix Algorithms

Matrix algorithms must be written to handle potentially undefined operations such as division by zero and the square root of negative real numbers. An algorithm must either avoid these operations or generate an error when such an operation is attempted.

Another problem of matrix algorithms is computation error. Usually, finite-precision arithmetic is used to represent real numbers [24, Section 2.4.1]. Since that

representation is finite, the representation is generally inaccurate. Each operation (especially addition and subtraction) on these numbers can increase the error (see Golub and Van Loan [24, Section 2.4]), and matrix algorithms must be written so that errors are kept under control.

For example, some matrix factorizations (including LU factorization) require pivoting [24, Section 3.4] to keep errors in the factorization to a minimum. Without pivoting (or other special steps), these factorizations can yield grossly inaccurate results. Algorithms for QR factorization are much better behaved since the factoring is done with orthogonal matrices which do not yield large computational errors (see Section 5.4.3).

## 1.5 Traditional Matrix Storage

The main memory of a computer is commonly indexed as a one-dimensional array. Mapping a multi-dimensional structure like a matrix into main memory is a matter of determining a total, linear order for all of the elements.

Traditionally, matrices have been stored in main memory using row-major order or column-major order. For a matrix using row-major order (column-major order), every row (column) of the matrix is kept contiguous in the memory of the computer [29, p. 298, 299]. Figures 1.4 and 1.5 give the indices for these two orders for a 4 × 4 matrix.

Poor spacial locality results from, for example, traversing a row-major matrix by columns instead of rows [11, Section 2], yet column traversals are often necessary in iterative algorithms. (The same applies to row traversals of column-major matrices.)

| 0  | 1  | 2  | 3  |

|----|----|----|----|

| 4  | 5  | 6  | 7  |

| 8  | 9  | 10 | 11 |

| 12 | 13 | 14 | 15 |

| 0 | 4 | 8  | 12 |

|---|---|----|----|

| 1 | 5 | 9  | 13 |

| 2 | 6 | 10 | 14 |

| 3 | 7 | 11 | 15 |

Figure 1.4: Row-major indexing

Figure 1.5: Column-major indexing

Better reuse of local memory (within a transfer block) is achieved by dealing with the matrix in terms of blocks as in Equation 1.2 for matrix multiplication. But since row-and column-major storage does not divide the matrix into contiguous blocks, a good algorithm must provide the blocking. One way to do this is by tiling the code [36, Section 20.4.3] (see Section 3.1).

# 1.6 The Quadtree Matrix

As suggested in Section 1.3.1, a divide-and-conquer data structure could be mapped into main memory using the divide-and-conquer paradigm. This section examines one such solution for a divide-and-conqueror data structure for matrices.

#### 1.6.1 Trees

**Definition 1.10** A tree is a finite set T of one or more nodes such that

1. there is one specially designated node called the root of the tree; and

2. the remaining nodes (excluding the root) are partitioned into  $m \geq 0$  disjoint sets  $T_1, T_2, \ldots, T_m$  and each of these sets in turn is a tree. The trees  $T_1, T_2, \ldots, T_m$  are called the subtrees of the root. [29, p. 308]

**Definition 1.11** The number of subtrees of a node is called the degree of that node. [29, p. 308]

**Definition 1.12** A node of degree zero is called a terminal node, or sometimes a leaf. [29, p. 308]

**Definition 1.13** The level of a node with respect to T is defined recursively: The level of root(T) is zero, and the level of any other node is one higher than that node's level with respect to the subtree of root(T) containing it. [29, p. 308]

There are three types of trees of particular interest:

**Definition 1.14** A binary tree is a tree where the degree of every non-terminal node is exactly two. A quaternary tree, or quadtree, is a tree where the degree of every non-terminal node is exactly four. An octernary tree, or octtree, is a tree where the degree of every non-terminal node is exactly eight.

Lewis and Denenberg [33, p. 101] define a useful term for binary trees that can be generalized for quadtrees and octtrees:

**Definition 1.15** All of the terminal nodes of a perfect tree are on the same level and all of the non-terminal nodes have maximum degree.

Figure 1.6: Level-order indexing of quaternary tree

#### 1.6.2 Quadtree Indexings

A quadtree can be indexed in a variety of ways. One way to index a quadtree is to index the nodes of the tree, level by level:

**Definition 1.16** The level ordering of a quaternary tree is an indexing of the nodes of the quaternary tree such that the root has index 0 and for a node in the tree with index i, its children are indexed 4i + 1, 4i + 2, 4i + 3, and 4i + 4. [47, p. 776]

Figure 1.6 is the level-order indexing of a quadtree with three levels. The nodes of one level of the tree are indexed from left to right in increasing order. Level l is indexed before level l+1.

Closely related to level-order indexing is Morton-order indexing.

**Definition 1.17** The Morton-order indexing of a quaternary tree is an indexing of the nodes of the quaternary tree such that the root has index 0 and for a node in the tree with index i, its children are indexed 4i + 0, 4i + 1, 4i + 2, and 4i + 3. [47, p. 776]

<sup>&</sup>lt;sup>4</sup>Traditionally, the root of a binary tree has index 1 in level-order indexing [29, p. 401]; however, in trees with a higher degree (such as a quadtree), there are gaps in the indexing from one level to the next. A 0-indexed root works well for all trees.

Figure 1.7: Morton-order indexing of quaternary tree

Figure 1.7 is the Morton-order indexing of a quadtree with three levels. The main difference between these two indexings is that level order gives an index to every non-terminal node while Morton order indexes each level starting with index zero. The result is that the level-order indices on one level of the tree differ from the corresponding Morton-order indices by only a constant [47]—the number of nodes in the higher levels of the tree. Specifically, on level l, a Morton-order index and its corresponding level-order index differ by

$$\sum_{i=0}^{l-1} 4^i = \frac{4^l - 1}{3}.$$

(1.3)

This conversion makes these indexings easily interchangeable.

Perfect quadtrees make complete use of the indexing space of Morton-order and level-order indexing. Imperfect trees can still be indexed with level order and Morton order using the 4i+c computations, but the "missing" subtrees leave gaps in sequential indexing.

$$M_1 = \left[ \begin{array}{ccc} 2.1 & 6.5 & 9.2 \\ 3.2 & 4.8 & 6.7 \\ 8.3 & 0.8 & 5.5 \end{array} \right]$$

$$\operatorname{pad}(M_1) = \begin{bmatrix} 2.1 & 6.5 & 9.2 & 0.0 \\ 3.2 & 4.8 & 6.7 & 0.0 \\ 8.3 & 0.8 & 5.5 & 0.0 \\ 0.0 & 0.0 & 0.0 & 0.0 \end{bmatrix}$$

Figure 1.8: Matrix  $M_1$

Figure 1.9: Matrix  $M_1$  padded

Figure 1.10: Quadtree matrix representation of  $pad(M_1)$

#### 1.6.3 Quadtree Matrix

**Definition 1.18** A quadtree matrix is either zero, a non-zero scalar, or a quadruple of sub-matrices (northwest, northeast, southwest, southeast) of equal size where at least one sub-matrix is non-zero. [46, p. 33]

The quadrants of a quadtree matrix are indicated with the arrow operator  $\downarrow$  (e.g.,  $M_1 \downarrow nw$ ,  $M_2 \downarrow ne \downarrow nw$ ); see Table 1.1.

The quadrant cleaving in the definition of the quadtree matrix suggests that the order of the quadtree matrix must be a power of two. The actual matrix may be padded with zeros to the south and east to bring its order up to a power of two. For example, the 3  $\times$  3 matrix  $M_1$  in Figure 1.8 is padded to a 4  $\times$  4 matrix in Figure 1.9. The corresponding quadtree for  $M_1$  is in Figure 1.10.

$$M_2 = \begin{bmatrix} 1 & 2 & 3 & 4 & 5 \\ 6 & 7 & 8 & 9 & 1 \\ 2 & 3 & 4 & 5 & 6 \\ 7 & 8 & 9 & 1 & 2 \\ 3 & 4 & 5 & 6 & 7 \end{bmatrix}$$

Figure 1.11: Matrix  $M_2$

Figure 1.12: Matrix  $M_2$  padded

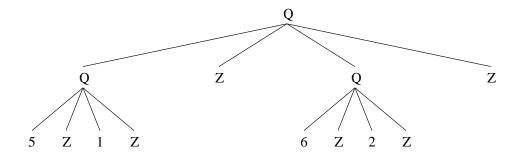

Figure 1.13: Quadtree matrix representation of  $\operatorname{pad}(M_2) \downarrow ne$

While the padding could be nearly three-quarters of the padded matrix, the zero matrix and the tree structure of the quadtree matrix definition allows for a logarithmic savings of the space and time that is devoted to storing and processing the padding. For example, Figure 1.12 is the 8  $\times$  8 padding of a 5  $\times$  5 matrix  $M_2$  given in Figure 1.11, and the northeast, southwest, and southeast quadrants are mostly padding. The potential savings is minimally demonstrated in the quadtree representation of the northeast quadrant of pad( $M_2$ ), given in Figure 1.13.

In quadrants within a matrix (never at the top level), global padding may extend into its west colonnade or its north stripe:

**Definition 1.19** Majority padding is padding that extends into the west colonnade or the north stripe. Minority padding is padding that is found only in the east colonnade or the south stripe. A perfect quadtree matrix is a quadtree matrix that has no padding.

A perfect quadtree matrix would be stored in a perfect quadtree (see Definition 1.15), hence the name.

The padded matrices  $pad(M_1)$  and  $pad(M_2)$ , Figures 1.9 and 1.12, respectively, have minority padding: padding only in the east colonnades and the south stripes of the top-level quadtree matrix matrix. The quadrant  $pad(M_2) \downarrow ne$  has majority padding since the padding extends into the west colonnade of that quadrant. Similarly,  $pad(M_2) \downarrow sw$  and  $pad(M_2) \downarrow se$  have majority padding.  $pad(M_2) \downarrow nw$  is a perfect quadtree matrix with no padding at all.

|         |        | Index  | Comput                 | ation                  |                        |

|---------|--------|--------|------------------------|------------------------|------------------------|

|         | Level  | 4i + 1 | 4i + 2                 | 4i + 3                 | 4i + 4                 |

|         | Morton | 4i + 0 | 4i + 1                 | 4i + 2                 | 4i+3                   |

| Z order |        | nw     | ne                     | sw                     | se                     |

| И order |        | nw     | $\mathbf{sw}$          | $\mathbf{n}\mathbf{e}$ | $\mathbf{se}$          |

| U order |        | nw     | $\mathbf{s}\mathbf{w}$ | $\mathbf{se}$          | $\mathbf{n}\mathbf{e}$ |

| C order |        | ne     | nw                     | $\mathbf{sw}$          | $\mathbf{se}$          |

Table 1.2: Correlation of quadrants to index computations

#### 1.6.4 Quadtree Matrix Implementation

A quadtree matrix can be viewed as a quaternary tree: the general case (i.e., the sub-quadrants) are non-terminal nodes; scalars and zero matrices are terminal nodes.

A strict interpretation of the definition of a quadtree matrix (Definition 1.18) is often implemented as a linked data structure with the zero matrix represented as a special terminal node, but as noted in Section 1.3.2, linked data structures suffer from data-locality deficiencies.

For better data locality, the nodes of a quadtree matrix can be put into an array (or arrays) of contiguous memory using an indexing for the quaternary tree. There are twenty-four (i.e., 4! = 24) different ways to correlate quadrant names (i.e., northwest, northeast, southwest, and southeast) and index computations (e.g., 4i+0, 4i+1, etc.). Table 1.2 lists four different ways to correlate quadrants and index computations. Often the application determines the best correlation. Z order is favored in the graphics community because pictures tend to be wide (more columns than rows). Then, if there were less than half as many rows as columns, it would be unnecessary to allocate space for the southern rows. Matrices often have more rows than columns,

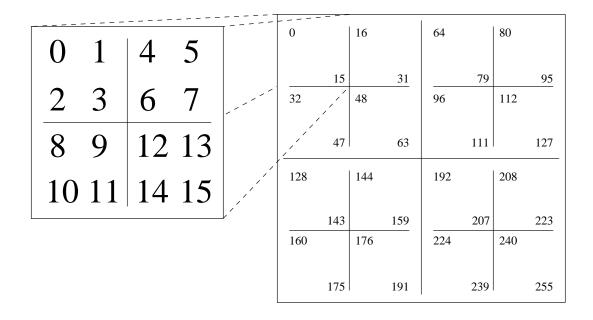

Figure 1.14: Morton ordering of a 16  $\,\times\,$  16 matrix with Z order

so M order is useful for matrices. Either order is equally useful for square matrices.

Figure 1.14 is the Morton order indexing of a  $16 \times 16$  matrix using the Z order.

With matrices padded to the south and east, it is best to index the southeast quadrants last. The padding will always be greatest in this quadrant, and the southeast most element of the unpadded matrix determines the amount of space that must actually be allocated since the padding that follows it is not necessary for the indexing to work correctly.

For example, consider the padded matrix  $pad(M_2)$  of Figure 1.12. A perfect  $8 \times 8$  matrix would require memory for 64 scalars; but with Z order,  $pad(M_2)$  only needs memory for 48 + 1 = 49 scalars since the Morton-order index of the southeast most element is 48. Only zeros are found at Morton indices 49 through 63. Unlike the

padding in the northeast and southwest quadrants of  $pad(M_2)$ , this padding in the southeast need not be allocated in the computer's memory. In general, the padding of the padded matrix might be asymptotically three-quarters of the matrix; but since the majority of the southeast quadrant would not be allocated, the padding will be only two-thirds, not three-quarters, of the total memory allocated. Avoiding the rest of the padding can be handled by decorating the matrices; as long as this memory is avoided, it only consumes address space, not valuable memory space.

#### 1.6.5 Decorating Quadtree Matrices

An initial concern with this sequential representation is the gaps left by the indexing of imperfect trees (as noted at the end of Section 1.6.2). The gaps in the address space caused by padding blocks makes the corresponding memory space unnecessary except as internal padding. If an algorithm avoids these gaps, they only waste address space and cheap, slow memory. These blocks will never be called into expensive, high-level cache.

To avoid this padding, quadtree matrix algorithms must recognize zero matrices high in the quadtree. Decorations can be used to represent zero matrices:

**Definition 1.20** An annotation describing the contents of a quadrant of a quadtree matrix is called a decoration. (See Wise [46, pp. 66, 67].)

For this work, there are four basic decorations: **zero**, **identity**, **dense**, and **un-known**.

• The **unknown** decoration (denoted as 'Q' in figures) indicates that the quadrant

has a mixture of dense, zero, and identity matrices, so the testing of decorations must continue as the sub-quadrants are traversed.

- The **zero** decoration ('Z') indicates that the quadrant is homogeneously zero. The algebra of the zero matrix can be used to control algorithms without descending into the quadrants.

- The **identity** decoration ('I') indicates that the quadrant is an identity matrix. Similar to the **zero** decoration, the algebra of the identity matrix can be used to control algorithms without descending into the quadrant.

- The dense decoration ('D') says that the quadrant is completely dense. There are not enough zero or identity blocks to test for them. All testing of decorations can be suspended for this quadrant.

#### 1.6.6 Storage Arrays

Since the decorations and elements of the matrix are different data types, two arrays are allocated:

- One array stores the decorations. The decorations are found in the non-terminal nodes of the quadtree, so the decoration array uses level-order indexing to store all of these nodes compactly. Given just the decorations in Section 1.6.5, two bits are sufficient to represent the decorations; eight bits were used since one byte is the smallest unit of memory easily accessed.

- One array stores the matrix elements. All of these elements are found at the leaf level of the quadtree, and so Morton-order indexing is used to store just

Figure 1.15: Level-order storage of  $pad(M_1)$  decoration (cf. Figure 1.9)

| 2.1 | 6.5 | 3.2 | 4.8 | 9.2 | 0.0 | 6.7 | 0.0 | 8.3 | 0.8 | 0.0 | 0.0 | 5.5 |  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  |  |

Figure 1.16: Morton-order storage of  $pad(M_1)$  scalars

these leaf elements. Each of these nodes requires eight bytes for double precision floating-point numbers.

The decoration matrix takes up comparatively little space. The element array at eight bytes for each element takes up twenty-four times as much memory as the decoration array at eight bits per decoration.

Level-order indices are needed to access the decoration array; Morton-order indices are needed to access the element array. Rather than traversing the nonterminal nodes with level-order indices and repeatedly converting them to Morton-order indices to access the element array, the pointer for the element array is offset using Equation 1.3. This pointer works as if the element array were allocated as level-order; but, in fact, the indices for nonterminal nodes should not be and never are used on the element array. This offset computation is done only once at the beginning of an algorithm.

Figures 1.15 and 1.17 depict the storage of the decoration trees for matrices  $pad(M_1)$  and  $pad(M_2) \downarrow ne$  from Figures 1.9 and 1.12, respectively. Both of these arrays use level-order indexing (in Z order) for the arrays; for  $pad(M_2) \downarrow ne$ , only the

| <br>Q | <br>Q | Z  | Q  | Z  |  |

|-------|-------|----|----|----|--|

| <br>2 | <br>9 | 10 | 11 | 12 |  |

Figure 1.17: Level-order storage of  $pad(M_2 \downarrow ne)$  decoration (cf. Figure 1.12)

| <br>5  | 0               | 1  | 0  | Т  | $\perp$ | $\perp$         | $\perp$ | 6               | 0  | 2  | 0               | 上  | Т  | 上  | $\perp$ |  |

|--------|-----------------|----|----|----|---------|-----------------|---------|-----------------|----|----|-----------------|----|----|----|---------|--|

| <br>16 | $\overline{17}$ | 18 | 19 | 20 | 21      | $\overline{22}$ | 23      | $\overline{24}$ | 25 | 26 | $\overline{27}$ | 28 | 29 | 30 | 31      |  |

Figure 1.18: Morton-order storage of  $pad(M_2 \downarrow ne)$  scalars

relevant portions of the array are given for that quadrant. Similarly, Figures 1.16 and 1.18 depict the storage of the scalars of the same matrices. These arrays are indexed using Morton-order indices (also in Z order), starting the array at index 0 for the northwest most elements. There is no need to represent the zero scalars in the scalar array because of the **zero** decoration, so that memory is not changed or even accessed.

## 1.6.7 A Divide-and-Conquer Data Structure

It is important to note how Morton-order and level-order indexing maps quadrants into an array: quadrants are in contiguous memory. This mapping into contiguous memory is done for *every* quadrant at *every* level of the quadtree. Furthermore, *every* level of the memory hierarchy on *every* machine will have some level of the quadtree matrix that fits into a transfer block of that level without using any special knowledge of the sizes of the transfer blocks.

Thus, in a practical sense, a transfer block is a quadrant.

Consequently, whatever is good for quadrants is good for transfer blocks. The particulars of the transfer blocks are irrelevant. As a programmer programs for quadrants, the programmer programs for all memory hierarchies.

## 1.7 Row Major Versus Morton Order

A high-performance algorithm should work for every level of the memory hierarchy. Row-major solutions<sup>5</sup> for handling the memory hierarchy, like tiling (see Sections 1.5 and 3.1), must be applied to the code for every level of the hierarchy. Tile the code once for primary cache and then for secondary cache and once again for virtual memory. When a new level is added, the code must be tiled again for the new level. When a level of the existing hierarchy is reconfigured (e.g., by adding more RAM), the tiling must change for the reconfigured level. When the code is ported to a new machine, the hierarchy is different, and so the tiling must be redone. All of these tiling changes mean changes to the code which necessitates recompiling. Furthermore, for each of these changes, the programmer or optimizing compiler must know the particulars about the memory hierarchy.

Solutions for quadtree matrices stored in Morton order<sup>6</sup> are simpler. A quadrant-friendly algorithm is written *once*. Since the quadrants are transfer blocks, a quadrant-friendly algorithm is implicitly friendly to transfer blocks. A recursive algorithm using quadrants at all levels of the quadtree will fit them—at some level—into the transfer blocks at each level of the memory hierarchy. When a level of the memory hierarchy is added or reconfigured, the mapping between quadrants and transfer blocks takes

<sup>&</sup>lt;sup>5</sup>Row major is equivalent to column major for these comments.

<sup>&</sup>lt;sup>6</sup>Similarly, Morton order and level order are equivalent for these comments.

care of the added or reconfigured level. When the code is ported to a new machine, the mapping between quadrants and transfer blocks handles the new hierarchy. The code is recompiled only for new processors, not for new memory hierarchies. Furthermore, since the mapping does not require any parameters, the programmer and compiler can be oblivious to the particulars of the memory hierarchy (i.e., being "cache-oblivious" [22]).

#### 1.8 Related Research

In his dissertation, Beckman [6] presents a (nearly pure) functional implementation of LU factorization for sparse matrices using a linked quadtree. He describes a distributed, shared-heap storage manager and a run-time system to execute LU factorization on sparse matrices in parallel on a shared-memory machine. The storage manager and run-time system are quite successful, but the performance of LU factorization is disappointing. Performance seems to be affected adversely by the poor compilation of recursion, the low payoff (i.e., one or two floating point operations) at each base case, and locality problems using a linked structure.

Wise [46] describes a more abstract and elaborate presentation of LU factorization. He concentrates on exact arithmetic matrix inversion (for use with discrete objects like integers and polynomials) and stresses the basic algebra of the algorithm that lends itself to a functional formulation. Wise uses decorations for directing the selection of a pivot matrix.

G. M. Morton introduced his indexing originally for geodetic databases [35]. The indexing is old and has been rediscovered several times. Samet [39] and others in the

graphics community use Morton-order indexing for storing and processing images.

Strassen [43] and Spieß [41] use a block decomposition of matrices to reduce the overall number of scalar multiplications for matrix multiplication. While reducing the flop count from  $O(n^3)$  to  $O(n^{\lg 7})$ , their algorithms requires extra space.

Chatterjee et al. explore some of the programming and compiler optimizations that can be done to make matrix multiplication run faster when using Morton order to store the scalar matrix [12, 11]. They chose a hybrid representation, using Morton order on the upper-level blocks and column-major for the base-case blocks. This allowed them to use BLAS routines (see below) for the base case. They found the hybrid awkward: either algorithms had to be rewritten for it or the data must be converted to and from other representations at a prohibitive cost.

Gustavson considers recursion and blocking for dense linear algebra [25]; Elmroth and Gustavson consider QR factorization in particular [18]. However, their recursive algorithm for QR factorization is in terms of columns (a single column is the base case for their recursion).

Golub, Plemmons, and Sameh [23] use a blocked algorithm for QR factorization in the context of the least-squares problem. Their matrices are sparse and patterned (block angular), obtained from geodetic computations.

Frigo, Leiserson, Prokop, and Ramachandran [22] study what they call *cache-oblivious* algorithms. Cache-oblivious algorithms are told *nothing* about the memory parameters of the machine that they run on, yet they still perform well with respect to the memory hierarchy. Their solution does not block the data representation, but it uses recursion on the existing representations (row- or column-major in the case of

matrices). By their definition, the algorithms developed here are cache-oblivious.

The BLAS (Basic Linear Algebra Subprograms) library [32, 17, 16] was written to implement basic matrix and vector operations (like matrix multiplication) as efficiently as possible for column- and row-major storage in both uniprocessor and parallel versions. The routines in this library are often tuned by manufacturers for their particular machines for even better performance.

LAPACK [2] is a high-performance library that implements high-level matrix algorithms like matrix factorizations. Many LAPACK algorithms use BLAS routines; other algorithms are written from scratch. The general algorithms are tuned for column- and row-major storage.

More recent work has been done on writing compilers that tune algorithms for traditional storage automatically. Both PHiPAC [7] and ATLAS [45] gather information (explicitly or through experimentation) to generate efficient code tuned for a specific machine. However, ATLAS only blocks for two levels of cache [45, p. 11]<sup>7</sup>.

#### 1.9 New Contributions

The duals for multiplication (see Section 3.2.1) for good cache behavior were first presented in Frens and Wise [20]. This dissertation is the first to analytically prove its good memory behavior (in Section 3.2.2).

Quadtree decorations themselves are not new. This work develops the use of decorations for matrix multiplication and QR factorization. In particular, the first

<sup>&</sup>lt;sup>7</sup>More recent reports about ATLAS available on the Web indicate that this has not changed since 1998 when this paper was written.

and last functions for matrix multiplication (see Sections 3.4.4 and 3.4.5) are new.

While Elmroth and Gustavson [18] present a similar QR factorization, their basic algorithmic unit (i.e., their base case) is still a column, not a block. The algorithms presented in Chapter 5 work on the quadrants of the matrix; this leads to a similar, but new and distinctive algorithm.

The parallel dispatch for parallel matrix multiplication was first presented in Frens and Wise [20]. The parallel dispatch for QR factorization is new.

# 1.10 Road Map

The next chapter lays out the playing field for this work. This includes discussions about this work as a proof-of-concept and the high-performance environment used to run these experiments including a description of the machines used to perform tests and a discussion of the compiler and timing issues involved with those tests.

Chapter 3 and 4 cover matrix multiplication. Chapter 3 covers the uniprocessor quadtree algorithm, including a proof of memory efficiency; Chapter 4 discusses a parallel implementation of this algorithm. The performances of both the uniprocessor and parallel algorithms are compared to the performances of comparable BLAS code.

Chapters 5 and 6 are organized similarly for QR factorization. Chapter 5 explores a quadtree matrix algorithm for QR factorization; the following chapter presents a parallel algorithm. The uniprocessor and parallel performances of the quadtree algorithms are compared to the performances of comparable LAPACK programs.

The final chapter offers conclusions and points to future work.

# **High-Performance Environment**

# 2.1 Proof of Concept

Any technology goes through several stages before it gains wide acceptance. Using functional programming and divide-and-conquer to develop high-performance algorithms is in an early stage. The purpose of this work is to give a proof-of-concept for the thesis that functional programming is an effective tool for solving high-performance problems. This proof-of-concept consists of two matrix problems: matrix multiplication and QR factorization. Matrix multiplication is simple and fundamental; QR factorization is more complex and is an important algorithm. Both classic algorithms for these problems have favorable error analyses [26, Sections 1.14.2, 3.5, and 18.5] so the quadtree algorithms were developed without consideration for error handling.

This work establishes an intermediate stage for a compiler. Ideally, a programmer would not write this code directly but instead would write pure functional code that

would be translated by a compiler with a knowledge of optimizing memory management. This work does not deal with such a translation, but instead concerns itself with what the target of such a translation should be.

# 2.2 Programming Liberties

Several liberties are taken with functional programming in order to compare performance with established high-performance computing results. Most functional programming languages depend on linked memory and a run-time garbage collector; this often hurts the performance of functional programs due to the time for collection and because linked structures have poor locality in general. If side-effects are permitted (strictly forbidden in pure functional programming), then the need for a garbage collector can be reduced, perhaps eliminated. The programs of this work manage memory on their own, allocating blocks of memory for the matrices and side-effecting the data in place. All matrices are uniquely referenced, so the side-effects are always safe. No new memory is allocated after the initial allocations, so there is no need for a garbage collector.

The algorithms were written in C to take advantage of the manufactures' optimizing compilers for their architectures. Supporting and driver code was written in C++.

The algorithms were also simplified by assuming that all matrices are square. In particular, this simplified the parallel dispatch considerations in Chapters 4 and 6. Rectangular matrices could be handled by extending the ideas presented in those chapters.

| System Property      | Value                                |

|----------------------|--------------------------------------|

| Number of processors | 10                                   |

| Type of processors   | R8000 (MIPS)                         |

| Clock speed          | 75 megahertz                         |

| Virtual memory       | 2 gigabytes                          |

| RAM                  | 2 gigabytes shared by all processors |

| Secondary cache      | 4 megabytes per processor            |

| Instruction cache    | 16 kilobytes per processor           |

| Data cache           | 16 kilobytes per processor           |

| Maximum mflop/s      | 300                                  |

The floating point unit of an R8000 is not connected to the primary cache and does not have one of its own; it is connected to the secondary cache [40, Section 2.2].

Table 2.1: System parameters of Power Challenge

#### 2.3 Machines

Four machines were used to run timing experiments: an SGI Power Challenge (Table 2.1), an SGI Octane (Table 2.2), a Sun Enterprise 450 Model 4400 (Table 2.3), and a Sun Ultra 5/10 (Table 2.4).

All of the tests were run on these machines in shared mode, although care was taken to run the tests when the load on the machines were minimal.

# 2.4 Compiler Issues

# 2.4.1 Compilers and Libraries

The MIPSpro compiler was used on the SGI machines. The manufacturer provided their own BLAS libraries; LAPACK was compiled locally. The Sun Workshop

| System Property      | Value          |

|----------------------|----------------|

| Number of processors | 1              |

| Type of processor    | R10000 (MIPS)  |

| Clock speed          | 195 megahertz  |

| Virtual memory       | 39.1 gigabytes |

| RAM                  | 128 megabytes  |

| Secondary cache      | 1  megabyte    |

| Instruction cache    | 32 kilobytes   |

| Data cache           | 32 kilobytes   |

| Maximum mflop/s      | 390            |

Table 2.2: System parameters of Octane  $\,$

| System Property      | Value                      |

|----------------------|----------------------------|

| Number of processors | 4                          |

| Type of processors   | UltraSparc II              |

| Clock speed          | $400~{ m megahertz}$       |

| Virtual memory       | 5.4 gigabytes, shared      |

| RAM                  | 2 gigabytes, shared        |

| Secondary cache      | 4 megabytes per processor  |

| Instruction cache    | 16 kilobytes per processor |

| Data cache           | 16 kilobytes per processor |

| Maximum mflop/s      | 400                        |

Table 2.3: System parameters of Enterprise 450

| System Property      | Value          |

|----------------------|----------------|

| Number of processors | 1              |

| Type of processor    | UltraSparc IIi |

| Clock speed          | 440 megahertz  |

| Virtual memory       | 1.1 gigabytes  |

| RAM                  | 256 megabytes  |

| Secondary cache      | 4  megabytes   |

| Instruction cache    | 16 kilobytes   |

| Data cache           | 16 kilobytes   |

| Maximum mflop/s      | 440            |

Table 2.4: System parameters of Ultra 5/10

Compiler 5.0 was used with the Sun Performance Library 2.0, which supplies both the BLAS and LAPACK libraries, on the Sun machines.

#### 2.4.2 Stride

The BLAS and LAPACK functions were tested with column major matrices. To avoid most problems with stride (see Golub and Van Loan [24, Section 1.4.4]), every array was allocated with an odd stride, even if the order of the matrix was even.

#### 2.4.3 Recursive Code

Since most optimizing compilers for C do not optimize recursion well, some optimizations for the quadtree algorithms were done by hand. Any of these hand-optimizations could be done by a recursion-aware optimizing compiler.

One hand-optimization was to store array pointers in global variables since they change infrequently (and only in the QR factorization). This greatly reduced the

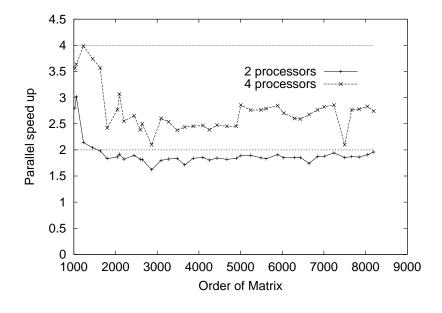

overhead incurred with the recursion.