# HARDWARE VERIFICATION USING COINDUCTIVE ASSERTIONS

#### Paul S. Miner

Submitted to the faculty of the Graduate School

in partial fulfillment of the requirements

for the degree

Doctor of Philosophy

in the Department of Computer Science

Indiana University

| Accepted by the Graduate   | e Faculty, Indiana University, in partial ful- |

|----------------------------|------------------------------------------------|

| fillment of the requiremen | ts of the degree of Doctor of Philosophy.      |

|                            |                                                |

|                            |                                                |

|                            | D. A. G. D. J. I.                              |

| Doctoral<br>Committee      | Prof. Steven D. Johnson<br>(Principal Advisor) |

|                            | ,                                              |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            | Prof. Daniel Leivant                           |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            | Prof. Jonathan W. Mills                        |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            |                                                |

|                            |                                                |

| August 13, 1997            | Prof. K. Jon Barwise                           |

|                            |                                                |

To Leah and Petra

## Acknowledgements

I wish to thank my advisor, Steve Johnson, for his steady support and extraordinary patience throughout the course of this research. His guidance helped make this journey a rewarding experience.

I am grateful to Daniel Leivant, Jonathan Mills, and Jon Barwise for expanding my knowledge. Each of them provided glimpses of intriguing research opportunities that I was unable to explore. I regret that I did not interact more closely with them during the course of my studies.

I had several interesting discussions about streams and coinduction with Larry Moss and Jean-Yves Marion. Larry's presentations about Hypersets at the Logic Group Seminar first inspired me to think about streams coinductively. Jean-Yves provided valuable input for the initial development of the streams library in PVS.

The Hardware Methods Laboratory provided a stimulating research environment during my two years in Bloomington. Bhaskar Bose first introduced me to the design derivation approach. Kamlesh Rath and Esen Tuna were instrumental in getting me up to speed using the design derivation system. Kathi Fisler frequently provided insightful observations. And I worked on interesting projects with both Shyam Pullela and Bob Burger. In addition to the research interactions, I will always value my

friendship with them and their families.

I have benefited from many stimulating interactions with my colleagues at NASA. In particular, Jim Caldwell, Victor Carreño, and Ben DiVito all provided encouragement and valuable feedback during this endeavor. I owe a special thanks to Ricky Butler for allowing me to pursue this opportunity and to NASA for making it possible.

Finally, to my wife Leah who walked every step of this journey with me and my daughter Petra who learned to walk as this journey neared its end, thank you for keeping me mindful of the important things in life.

#### Abstract

Systems of mutually recursive stream equations provide a concise model of digital hardware designs. The formal design algebra presented by Johnson illustrates the utility of this representation for design derivation. The design derivation approach has been mechanized by Bose and applied to significant case studies. However, a design optimization sometimes depends upon the semantics of the implemented function. This cannot be captured within the design algebra. Design derivation needs to be augmented with additional verification strategies.

The stream equations employed in the design derivation approach are an instance of definition by corecursion. Therefore, the design derivation approach may be augmented using proof by coinduction. Coinduction is a useful strategy for proving that two sequential hardware designs have the same behavior. This enables safe substitution of an innovative optimization into a mature design. Furthermore, coinduction is useful for establishing that a signals within a design satisfy invariant properties. Such invariants, called coinductive assertions, are essential to ensure the validity of aggressive design optimizations.

This dissertation illustrates how design derivation is augmented using the Prototype Verification System (PVS). A PVS library to provide the basic declarations needed for reasoning about streams is developed. Stream equations are defined using

corecursion, and equality between streams is proven using coinduction. The combination of derivation-based and theorem prover-based verification is illustrated using two significant examples. First, a fault-tolerant clock synchronization circuit, suitable for use in critical applications, is developed using this combined approach. A clever optimization that reduces the chip area is verified using coinductive proof within PVS. The second example is the development of an architecture for floating-point division. A number of optimizations that reduce the cycle time of the inner loop of the algorithm are verified using the combined approach.

## Contents

| $\mathbf{A}$   | ${f A}{ m cknowledgements}$ |                                          | iv |

|----------------|-----------------------------|------------------------------------------|----|

| $\mathbf{A}$   |                             |                                          | vi |

| 1 Introduction |                             | oduction                                 | 1  |

|                | 1.1                         | Contributions                            | 6  |

|                | 1.2                         | Outline of the Presentation              | 7  |

| 2              | Rel                         | ated Research                            | 11 |

|                | 2.1                         | Overview of Design Derivation            | 11 |

|                | 2.2                         | Overview of PVS                          | 13 |

|                | 2.3                         | Research in Hardware Verification        | 17 |

|                |                             | Theorem-Prover based System Verification | 17 |

|                |                             | Algebraic Approaches                     | 19 |

|   | 2.4  | Coinduction and Corecursion                | 21 |

|---|------|--------------------------------------------|----|

| 3 | Rea  | soning about Streams                       | 23 |

|   | 3.1  | Stream Basics                              | 23 |

|   | 3.2  | Defining Streams in PVS                    | 33 |

|   |      | Proof of stream equality using coinduction | 38 |

|   |      | Invariants on Streams                      | 39 |

|   |      | Coinductive Proofs using PVS               | 40 |

|   |      | Advanced examples of stream definition     | 48 |

| 4 | Stre | eams as a representation of Hardware       | 51 |

|   | 4.1  | Simple Examples                            | 55 |

|   |      | Factorial                                  | 55 |

|   |      | Fibonacci                                  | 57 |

|   | 4.2  | Coinductive Proofs about Hardware          | 58 |

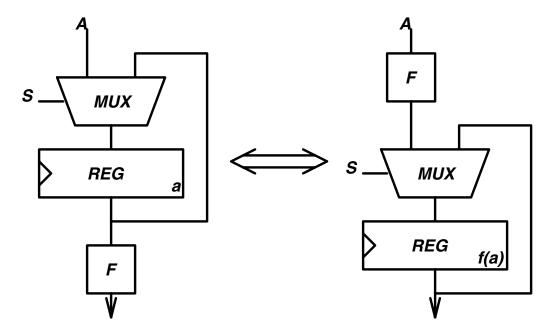

|   |      | Retiming Transformation                    | 59 |

|   |      | Behavioral Abstraction                     | 60 |

|   |      | Temporal Abstraction                       | 62 |

| 5 | Fau  | lt-Tolerant Synchronization                | 67 |

|   | 5.1                                           | Top-Level Properties                                 | 68                    |

|---|-----------------------------------------------|------------------------------------------------------|-----------------------|

|   | 5.2                                           | The Verified Algorithm                               | 68                    |

|   | 5.3                                           | Behavioral Specification                             | 70                    |

|   | 5.4                                           | Initial Derivation                                   | 75                    |

|   | 5.5                                           | An Optimization                                      | 82                    |

|   |                                               | Verification                                         | 86                    |

|   | 5.6                                           | Establishing Invariants                              | 90                    |

|   | 5.7                                           | Another verification of the optimization             | 92                    |

|   | 5.8                                           | VLSI implementation                                  | 93                    |

|   |                                               |                                                      |                       |

| 6 | Floa                                          | ating Point Division                                 | 95                    |

| 6 | <b>Floa</b> 6.1                               | ating Point Division  IEEE Floating-Point Arithmetic | <b>95</b>             |

| 6 |                                               |                                                      |                       |

| 6 | 6.1                                           | IEEE Floating-Point Arithmetic                       | 96                    |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | IEEE Floating-Point Arithmetic                       | 96<br>96<br>99        |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | IEEE Floating-Point Arithmetic                       | 96<br>96<br>99        |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | IEEE Floating-Point Arithmetic                       | 96<br>96<br>99        |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | IEEE Floating-Point Arithmetic                       | 96<br>96<br>99<br>103 |

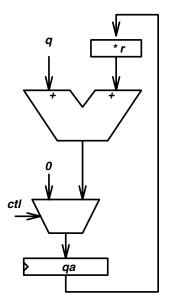

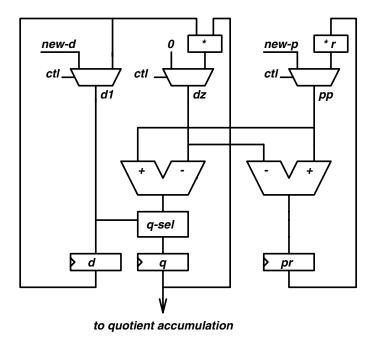

|   |     | On-the-fly Quotient Accumulation | 117         |

|---|-----|----------------------------------|-------------|

| 7 | Con | nclusions                        | <b>12</b> 4 |

|   | 7.1 | Limitations of the Approach      | 125         |

|   | 7.2 | Suggestions for Future Work      | 126         |

|   | 7.3 | Concluding Remarks               | 128         |

## List of Figures

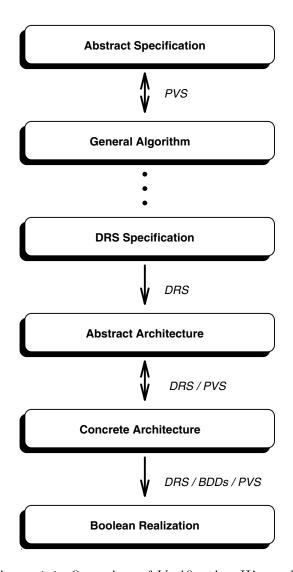

| 1.1 | Overview of Verification Hierarchy                 | 3  |

|-----|----------------------------------------------------|----|

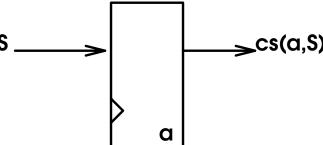

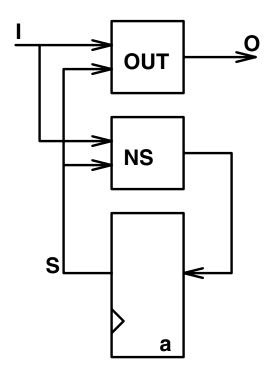

| 4.1 | Standard model of Sequential System                | 52 |

| 4.2 | Simple Retiming Transformation                     | 60 |

| 4.3 | Simple Counter Circuit                             | 61 |

| 4.4 | Stuttering Counter Circuit                         | 63 |

| 4.5 | Simple Counter Circuit                             | 64 |

| 4.6 | Fair Counter                                       | 65 |

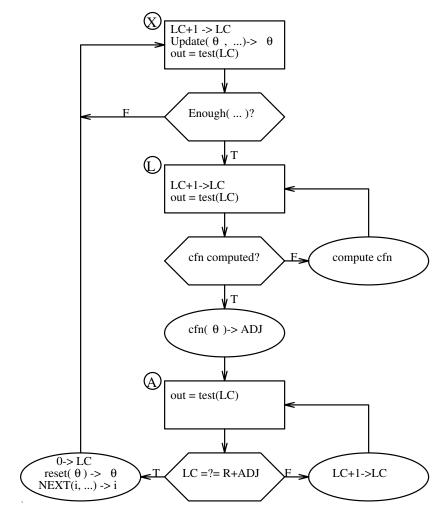

| 5.1 | ASM Chart for General Algorithm                    | 71 |

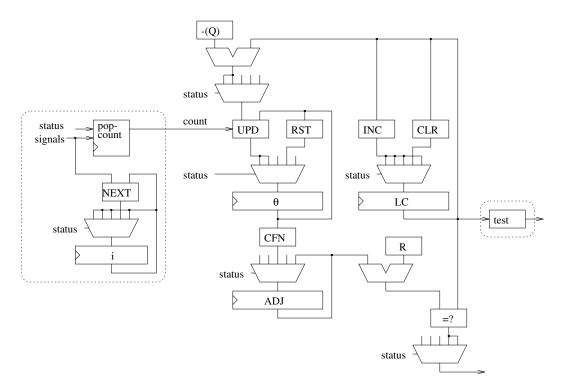

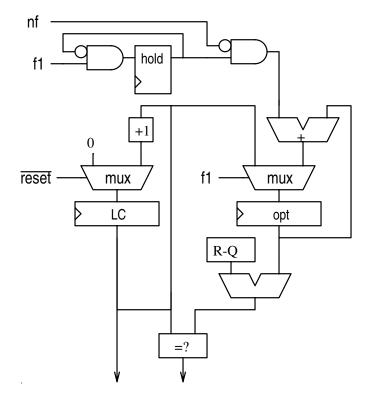

| 5.2 | Initial Architecture                               | 74 |

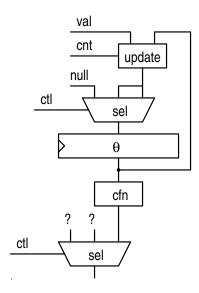

| 5.3 | Refined sub-circuit prior to ad hoc transformation | 75 |

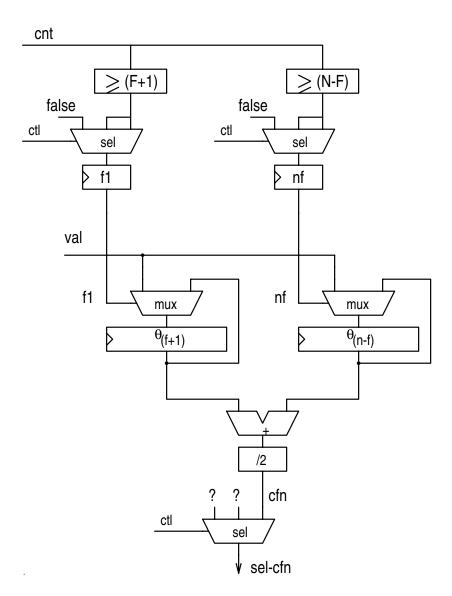

| 5.4 | Refined sub-circuit after ad hoc transformation    | 83 |

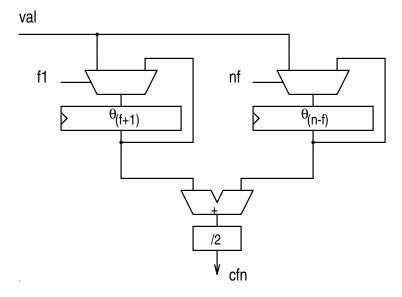

| 5.5 | Core Circuit for Computing Convergence Function    | 84 |

| 5.6 | Optimized Convergence Function                       | 85  |

|-----|------------------------------------------------------|-----|

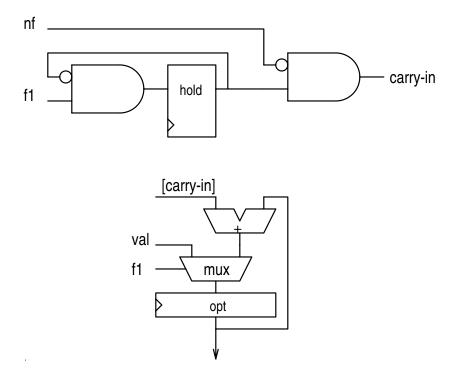

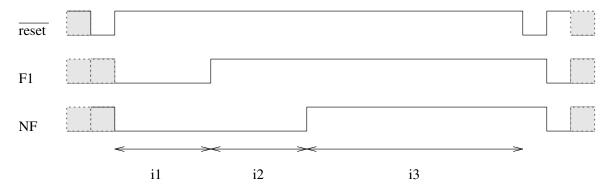

| 5.7 | Signal Assumptions                                   | 86  |

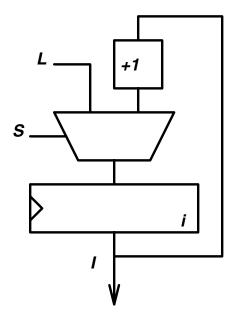

| 5.8 | Counter Sub-Circuit                                  | 90  |

| 5.9 | Core Synchronization Circuit                         | 94  |

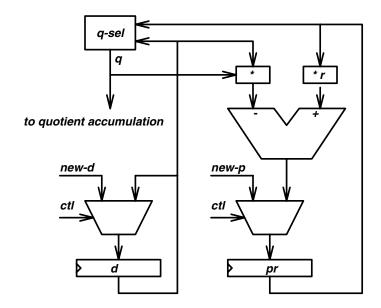

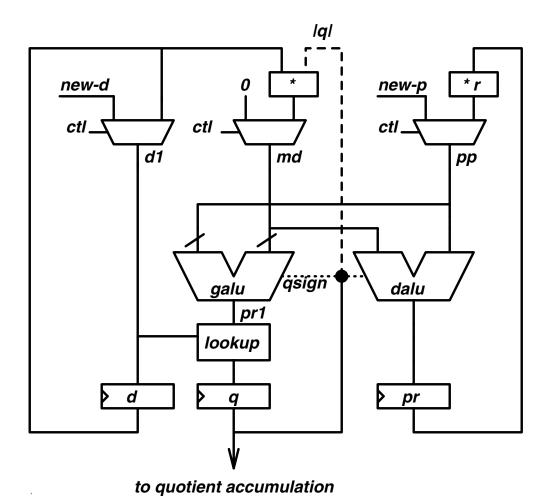

| 6.1 | Initial Partial Remainder Sub-Circuit                | 102 |

| 6.2 | Initial Quotient Accumulation Sub-Circuit            | 102 |

| 6.3 | Derived Architecture                                 | 106 |

| 6.4 | Final Partial Remainder Sub-Circuit                  | 109 |

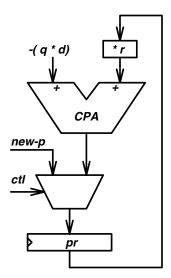

| 6.5 | Partial Remainder Using a Carry-Propagate Adder      | 111 |

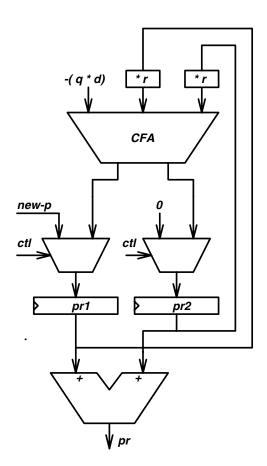

| 6.6 | Redundant Partial Remainder Using a Carry-Free Adder | 112 |

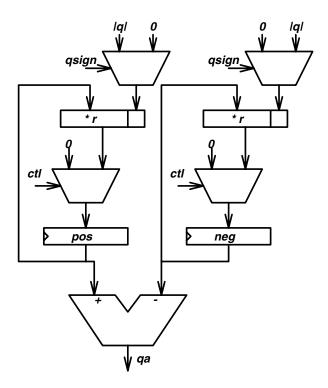

| 6.7 | Redundant Representation of Accumulated Quotient     | 115 |

Approaches to hardware development need to include an efficient means to represent and reason about changes in an evolving hardware design. As a hardware design matures, performance and area requirements evolve, also. The resulting changes to the design typically complicate verification activities. A verification environment must be flexible enough to accommodate a changing design.

Systems of mutually recursive stream equations provide a concise model of digital hardware designs. The formal design algebra presented in Johnson's Dissertation illustrates the utility of this representation for design derivation [Joh84]. The design derivation approach has been mechanized by Bose and applied to significant case studies [Bos94]. However, a design optimization sometimes depends upon the semantics of the implemented function. This cannot be captured within the design algebra. Design derivation needs to be augmented with additional verification strategies.

The representation of hardware via stream equations may be exploited. The stream equations employed in the design derivation approach are an instance of definition by *corecursion*. Therefore, the design derivation approach may be augmented

using proof by coinduction. Coinduction is a useful strategy for proving that two sequential hardware designs have the same behavior. This enables safe substitution of an innovative optimization into a mature design. Furthermore, coinduction is useful for establishing that a signals within a design satisfy invariant properties. Such invariants, called coinductive assertions, are essential to ensure the validity of aggressive design optimizations.

As technology improves it is possible to incorporate increasingly complicated functions in hardware. Analysis of the resulting designs is infeasible without mechanized support. In this research, I have used two tools: The Prototype Verification System (PVS [ORSv95]) and the Derivational Reasoning System (DRS [BTC96]). PVS is a general purpose mechanical theorem proving system; it provides a rich specification language and a powerful interactive theorem proving environment. DRS is an interactive formal design tool that allows a designer to derive a hardware design from an abstract behavioral level description. A design is produced by a series of transformations that ensure the final artifact is consistent with the initial behavioral description. That is, the design is correct-by-construction. Derivation-based formalisms provide a suitable framework for managing routine design refinements, but cannot be expected to cover the possible design space. General purpose theorem proving systems, on the other hand, provide sufficient generality to capture arbitrary design refinements, but can be cumbersome for the more routine aspects of design. Formal design environments should accommodate both approaches.

Design verification spans several levels from a mathematical statement of requirements to a detailed design. The verification hierarchy, annotated with choice of verification tool, is depicted in Figure 1.1. At the top level is a mathematical statement of properties that the design should satisfy. These requirements may be expressed in several different ways, depending upon the nature of the problem. Algorithms over

Figure 1.1: Overview of Verification Hierarchy

abstractly defined datatypes are proven to satisfy the top level requirements. Without knowledge of what the requirements may be, the only logical choice of tool for this verification activity is a general purpose theorem proving system such as PVS. General algorithms are transformed into behavioral level descriptions. In the figure, this relationship is depicted with ellipses because there is currently a semantic gap between the algorithm definition in PVS and a DRS behavioral level description. Within DRS, a behavioral description is refined until the designer is satisfied with the control structure of the design, then it is transformed into an initial architectural specification. At this stage, the architecture is refined to a concrete design. Most architectural refinements are performed within DRS. However, transformations that exploit the semantics of user defined functions may require external justification. These are verified using PVS. Finally, the abstract types in the design are instantiated with bit-vector representations. This may expose additional opportunities for refinement and optimization, so more structural transformations may be performed at this level. The resulting design is now entered into a commercial CAD tool for realization in hardware.

The case studies presented in Chapters 5 and 6 explore each level of refinement depicted in Figure 1.1. However, the primary emphasis is on the design phase between an abstract architectural description and a concrete architecture. At this stage, the principal design tool is DRS. The design is described by a system of mutually recursive stream equations. Algebraic transformations on this system of equations are used to refine the design to a target architecture. However, there are design optimizations that may not be effectively realized within a transformational system. In particular, there may be refinements that are only applicable within the context of a specific design. Such transformations cannot be justified on general principles. I

adopt the terminology of Saxe, et al. [SGGH93] and refer to these as *ad hoc* refinements. Justification of such refinements requires external verification. Thus, there is a need to augment the derivational approach with mechanical theorem proving support, thereby enabling effective formal development of efficient hardware.

In order augment this stage of design with theorem proving support, we need to determine how to represent DRS circuit descriptions within PVS. There are two approaches. A deep embedding of DRS into PVS would consist of encoding the DRS syntax within PVS and defining a semantic interpretation. A shallow embedding consists of directly encoding DRS objects as PVS objects. Deep embeddings have the advantage of being able to support meta-level reasoning, but require working through a layer of interpretation. The intended application of this work is to use PVS as a verification engine supporting hardware design using DRS. A shallow embedding is a more direct way to achieve this goal.

The final problem is to determine how to represent DRS descriptions of sequential systems within PVS. There are several models of sequential systems in the mechanical theorem proving literature. Most use a representation similar to that advocated by Gordon [Gor86]. Signals are represented as functions from natural numbers to the signal type, hardware components are defined as relations between input and output, and hardware structure is captured by relation composition. This representation was considered for theorem-prover based justification of ad hoc refinements. However, within DRS, connections between combinational logic blocks are represented by function composition and the sequential aspect of the design is captured using stream equations. Feedback in the sequential circuit design is naturally represented by feedback in the stream equations. This is an instance of definition by corecursion [BM96]. Just as definition by recursion gives rise to proof by induction, the dual notion of corecursive definition gives rise to proof by coinduction. This proof technique simplifies

the verification of sequential hardware designs.

#### 1.1 Contributions

The primary contribution of this research is the development and demonstration of a robust method for showing equivalence between two sequential circuits. The approach is based upon the observation that definition by corecursion is a natural representation for sequential hardware. This representation is especially useful in mapping an abstract behavioral level description to a register-transfer level (RTL) design. In addition, one can exploit this representation both to express and to verify properties of a design. Signals within the circuit are defined using corecursive stream equations. These signals are shown to satisfy invariant properties by coinduction. Such invariants are called coinductive assertions. Sub-circuits are shown to have equivalent behavior with respect to these coinductive assertions by exhibiting a suitable stream bisimulation.

Another contribution is the exploration of the heterogeneous reasoning required to support the application of complementary approaches to the design verification problem. Theorem proving and design derivation are just two of many tools available for design and verification. While it is possible to use a general purpose theorem proving system to support all stages of the design process, much of the design process consists of manipulation of large syntactic objects. These manipulations are routine, and do not require the deductive power of a general purpose theorem prover. In addition, most general purpose theorem provers do not handle large syntactic objects in a computationally efficient manner. Thus we need to address the interaction between design tools and general purpose verification tools.

In the work presented here, the design derivation tools represent sequential hard-ware using systems of stream equations. Reasoning about systems of stream equations within a general purpose theorem prover requires construction of an appropriate model. Within PVS, I have developed a theory of streams that allows definition by corecursion and proof by coinduction. This combination of design and verification tools is illustrated on two significant examples: a clock synchronization circuit and a floating-point division unit. In both cases, coinductive proofs are employed to verify circuit optimizations.

#### 1.2 Outline of the Presentation

Chapter 2 provides an overview of the two mechanized reasoning systems employed in this research. The design derivation tool DRS provides a mechanized collection of transformations that enable a designer to develop a hardware design that is correct by construction. The mechanical theorem proving system PVS provides reasoning support for general results. It also enables exploration of verification strategies. The basic features of each tool are reviewed to provide a foundation for the discussion in the remainder of the dissertation. The chapter closes with a survey of related research.

An overview of streams, illustrated with some simple examples, is presented in Chapter 3. The primitive operations on streams are introduced and illustrated. A formulation of streams as a coinductive type in PVS is presented. The basic definitional forms are presented and coinductive proof techniques are justified. The development of a general strategy for automating coinductive proofs is illustrated using several examples from *Vicious Circles* [BM96].

Systems of stream equations provide a concise model of digital hardware. Chapter 4 illustrates the use of stream equations to represent sequential hardware design descriptions. A shallow embedding of DRS style stream equations in PVS is developed. The technique is illustrated with a few sample circuits. Chapter 4 concludes with an illustration of basic techniques for reasoning about digital hardware using coinduction. Several simple hardware verification problems are presented.

Chapter 5 presents the development of a fault-tolerant clock synchronization circuit. This development is a multi-level verification effort. It spans the spectrum from abstractly stated high-level properties to a VLSI implementation. The routine architectural refinements are performed within DRS. Two ad hoc refinements to the derived architecture are verified using coinductive proof in PVS. The first ad hoc refinement consists of a change in representation of the mechanism used to capture readings from remote clocks. An abstract storage device with a list-based representation is replaced by a pair of registers. The second refinement is a clever optimization to the core synchronization sub-circuit. Properties of the surrounding design make it possible to compute the same function using a more compact circuit. The chapter concludes with an illustration of the flexibility of the approach, by expanding the scope of the verification to explicitly include some of the surrounding design.

Chapter 6 illustrates a different class of optimization in the verification of a floating-point division unit. Performance is a key concern in the development of floating-point hardware. One way to improve performance in synchronous digital hardware design is to minimize the critical path, that is, reduce the number of combinational logic gate delays between any two clocked storage elements. There are a number of options at the designers disposal. One alternative is to re-time a design so that the gate delays are more uniformly distributed throughout the design [LS91]. Another technique is to introduce redundant representations for certain data items to

reduce the number of gate-delays required. Each optimization is illustrated within the design framework depicted in Figure 1.1. Coinductive verification provides a powerful technique for justifying these optimizations.

The focus of this dissertation is hardware design verification, that is, the goal is to establish that a design expressed in a hardware description language (HDL) is consistent with its specification. When design verification fails, as it did for the floating-point divide unit of the Intel Pentium(TM) microprocessor, the cost can be enormous. The bug in the Pentium cost Intel nearly \$500 million [Pra95]. Digital systems are increasingly being used for life-critical applications. A design error in a system controlling an aircraft or nuclear reactor can have dire consequences. The maiden flight of the Ariane-5 launch system ended prematurely in a spectacular fireworks display. The cause was attributed to a software design error in the inertial reference system [Ari96]. The cost of the payload lost in the mishap was estimated at approximately \$500 million [SD96]. Thus, two design errors account for a financial loss approaching one billion dollars.

We need robust techniques for design verification. Historically, the primary approach for design verification has been simulation. An executable model of the design is constructed, and this model is exercised with a series of test cases. However, even for designs of moderate complexity, it is infeasible to fully test the design with this approach. To address future design verification requirements, new techniques must be developed. In fact, Keutzer identifies design verification as the most urgent problem in [integrated circuit (IC)] design [Keu96].

The design derivation approach provides an exceptional framework for hardware design. The design space can be explored in a rigorous manner, secured by the knowledge that the design is correct by construction. Furthermore, the representation of hardware using corecursive stream equations allows for the augmentation of design

derivation with coinductive verification strategies. This provides an opportunity to verify aggressive optimizations that exploit the semantics of the implemented function.

#### 2.1 Overview of Design Derivation

The design derivation tools DDD [Bos91, Bos94] and DRS [BTC96] implement a formal design algebra for developing correct digital circuit descriptions. The designer interactively transforms high level behavioral specifications into a description suitable for entry into hardware synthesis tools. The top level describes the intended behavior of the circuit using a collection of mutually recursive function definitions in tail form. Each function corresponds to a control state; arguments to the functions represent the visible storage elements of the design. Transformations at this level allow the designer to modify the control structure of an architecture while preserving the functional correctness, relative to synchronization constraints. Once the control structure is determined, DRS automatically transforms the behavioral specification into an initial architectural level description. This description is refined using structural level transformations that allow the designer to reorganize the design to correspond to typical hardware design constructs. Once the architecture is refined,

the signals and operations are mapped to bit-vector representations. Depending upon the target technology (e.g. Field Programmable Gate-Array or custom VLSI), additional refinements are performed at this level to determine the physical organization of the design.

The design derivation tools represent the structure of a digital system using a collection of mutually recursive stream equations. A stream is an infinite sequence of uniformly typed values,

$$X = [x_0, x_1, x_2, \ldots]$$

The stream constructor 'cs' adds an element to the front of the sequence

$$\mathtt{cs}(z,X) = [z,x_0,x_1,x_2,\ldots]$$

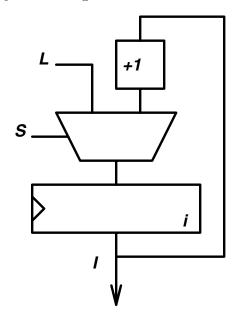

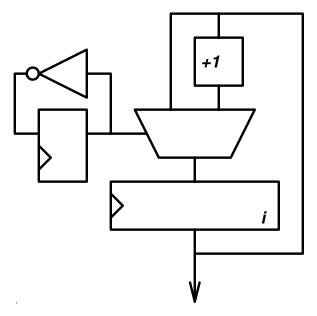

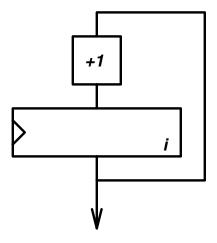

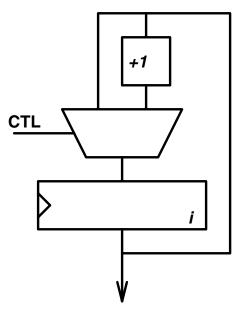

Function 'cs' models a storage element. The first argument is the current value and the second is the input stream. Functions on values lift to sequences so that f(X,Y) denotes  $[f(x_0, y_0), f(x_1, y_1), ...]$ . DRS uses a system of equations to define a network of streams; recursion represents feedback in the circuit. For example, the following equation represents a loadable counter circuit.

$$COUNT = cs(i, MUX(S, L, INC(COUNT)))$$

(2.1)

where i is the current integer value of the counter, INC and MUX are the increment and selection functions lifted to streams, and streams S and L are the multiplexor select signal and load input respectively. Within DRS, free variables in a system of stream equations must be bound by a system level abstraction. This abstraction defines the input signals for the circuit. The circuit's output is a subset of the streams named in the system of equations.

Several significant hardware designs have been developed using DDD. In particular, Bose has formally derived the DDD-FM9001 [Bos94, BJ93] processor from Hunt's formal specification of the mechanically verified FM9001 microprocessor [Hun92]. Another significant derivation is the development of a Scheme Machine, which consists of a garbage-collecting memory system and a CPU that executes high-level Scheme primitives [Bur94]. During the above projects, it was recognized that a combination of design derivation with mechanized proof support would be superior to either approach individually [JWB89]. In the current study, hardware design using DRS is augmented using the PVS theorem proving system.

#### 2.2 Overview of PVS

PVS is a general purpose specification and verification system developed at SRI International [ORS92, ORSv95]. The PVS specification language is based on higher-order logic. Specifications consist of collections of theories that may be parameterized by types and constants. Theory parameters may be constrained by conditions. PVS has predicate subtyping and dependent types. Since types may be constrained by an arbitrary predicate, typechecking is undecidable. When the typechecker cannot determine if an expression is correctly typed, it automatically generates proof obligations called Type Correctness Conditions (TCCs). PVS includes typing judgements to help reduce the frequency of TCCs. Included with PVS is the *prelude*, a collection of theories containing definitions and basic results.

There are two primitive types: boolean and number. The type boolean has the usual properties. The type number is different from the numeric types in other mechanical theorem proving systems. Properties of number are either declared in the

PVS prelude or hard-coded in the PVS typechecker and prover. The type number is declared as a nonempty, uninterpreted type. PVS recognizes all Arabic numerals as constants of type number. In addition, the fact that distinct numerals represent distinct numbers is hard-coded in the PVS prover. The type real is declared as a non-empty subtype of number. There are implicit typing judgements that assert that all Arabic numerals also have type real. The arithmetic operators and order relations are defined over the reals, and are known by the PVS decision procedures. Since PVS requires all functions to be total, the type of the division operator is constrained so that the divisor is nonzero. This uses the predicate subtyping mechanism. The type of nonzero reals is declared as follows:

#### nonzero\_real: NONEMPTY\_TYPE = {r: real | r /= 0} CONTAINING 1

The containing clause is not necessary, but it simplifies the proof of the TCC that results from this declaration. With the containing clause, this declaration generates the proof obligation:  $\vdash 1 \neq 0$ . This is known to the prover and is automatically discharged. If the containing clause were omitted, this declaration would generate the obligation:  $\vdash \exists r.\ r \neq 0$ . A proof of this goal requires user interaction. The usual properties of the real numbers are either expressed as axioms, or are coded in the linear arithmetic decision procedures built-in to the PVS prover. The field axioms are known by the decision procedures, as are the linear order axioms. The remaining axioms are declared in the prelude theory real\_axioms.

The rationals are a nonempty, uninterpreted subtype of the reals (and by transitivity, also a subtype of number). Again, the fact that Arabic numerals have type rational is coded into PVS. Axioms in prelude theory rationals assert that the rationals are closed under addition, subtraction, multiplication, and division (with the divisor restricted to nonzero rationals). Similarly, the integers are defined as an

uninterpreted subtype of the rationals (again containing the Arabic numerals). Axioms in prelude theory integers assert that the integers are closed under addition, subtraction, and multiplication. Finally, the natural numbers are declared as the predicate subtype of nonnegative integers.

PVS includes the usual function type constructor, as well as constructors for tuple and record types. PVS also includes dependent forms of these. Dependent types have a number of uses within a verification system like PVS. For example, consider the floor function which truncates a real number x to the nearest integer  $\leq x$ . In the PVS prelude, this function is defined as follows:

```

floor(x:real): {i:int | i <= x & x < i + 1}

```

That is, floor is a constant with type  $[x:real \rightarrow \{i:int \mid i \le x \& x < i + 1\}]$ . This type declaration uniquely defines the floor function. In PVS, this declaration spawns the proof obligation:  $\vdash \forall x. \exists i. i \le x < i + 1$ . By encoding the desired behavior into the type, this information is available to the decision procedures. Many standard facts about the floor and ceiling functions are automatically discharged by the PVS decision procedures.

Dependent types are also quite useful in hardware verification, where many functions have regular structures that are parameterized by the width of the data word. Hanna was the first to advocate dependent types for this purpose [HD92]. PVS allows parameterized type declarations, inspired by the VERITAS<sup>+</sup> system [HDL89]. The PVS prelude includes the following parameterized type declaration:

```

below(i): TYPE = \{s: nat \mid s < i\}

```

Using this type, we can declare a bit to have type below(2). The type of n-bit words

can be declared as:

```

word(n) : TYPE = [below(n) -> bit]

```

Use of this parameterized type is illustrated by the following declaration for byte:

```

byte: TYPE = word(8)

```

PVS also has a mechanism for defining recursive abstract datatypes that are freely generated by a set of constructors [OS93]. The abstract data mechanism generates a theory which declares an uninterpreted type constrained by a number of axioms. These axioms correspond to the properties that would arise from the *least* solution to the recursive type equations. PVS does not yet have a corresponding mechanism for corecursive datatypes.

PVS provides an interactive theorem proving environment using a Gentzen style sequent calculus presentation of the proof goals. At the core of PVS's prover is a collection of decision procedures combined using a technique developed by Shostak [Sho78, Sho84, CLS96]. This eases some of the more burdensome aspects of interacting with a mechanical theorem prover. Most simple arithmetic results are discharged by invoking the decision procedures. The user rarely needs to direct the prover when faced with simple facts of arithmetic. PVS has a powerful conditional rewriter. There is a strategy language similar to LCF-style tactics. Thus, the user can define high-level proof procedures. There are several powerful strategies distributed with PVS that automatically verify a large number of results. For example, the built-in proof strategy (grind) is sufficient powerful to automatically verify many goals. The strategy (induct-and-simplify) is the brute force strategy for automating simple proofs by induction. PVS allows the user to prove lemmas in any order. It maintains a proof

dependency analysis to ensure that all obligations have been discharged. Included in the analysis is an enumeration of all axioms used by the proof chain.

There have been a number of exercises integrating various styles of reasoning within PVS. The most recent presentation of these efforts is reported in [ORS97].

#### 2.3 Research in Hardware Verification

There are several competing approaches for formalizing the design process. At one end of the spectrum are general purpose mechanical theorem proving systems with expressive languages. Frequently, these systems require human interaction to produce machine checked proofs. At another extreme are a collection of fully automatic tools that can be applied to specialized verification problems. These tools include tautology checking using Binary Decision Diagrams [Bry86] and, more recently, model checking techniques for state machine verification [CES86, BCM<sup>+</sup>92, BCL<sup>+</sup>94].

#### Theorem-Prover based System Verification

There are several significant examples of theorem-prover based verifications in the literature. Examples include microprocessors [Hun92, SM95], dedicated hardware for fault-tolerance [BY90, SB91], and many efforts in floating-point verification [BKM96, CGZ96, RSS96, OLHA94, LO95, VCD94, Har95]. Theorem prover based verifications are not always robust in the face of changes. A small change in the design may invalidate much of the correctness proof [Wil97].

A notable effort is Hunt's verification of the FM9001 processor using nqthm [Hun92].

Hunt's verification strategy consists of a simulation model that animates designs expressed in a hardware description language. The verified design was subsequently fabricated in a VLSI implementation. The verification approach has subsequently been used successfully on commercial hardware devices [BKM96]. Another significant effort is the verification of the microcode of a set of instructions of the Rockwell-Collins AAMP5 microprocessor in PVS [SM95]. The AAMP5 is a modern microprocessor designed for aerospace applications. The verification activity uncovered some errors that had been seeded in the microcode to test the effectiveness of theorem proving techniques.

Prior to the design error in the Pentium processor, there were only a few activities focussed on design verification of floating-point hardware. The first efforts targeted verified implementations of binary non-restoring algorithms. Leeser, O'Leary, et al. present a verification, using Nuprl, of a binary non-restoring square root algorithm and its implementation [OLHA94, LO95]. Verkest, et al. present a similar verification, using ngthm, of a binary non-restoring division algorithm [VCD94]. In response to the flaw in the Pentium, several researchers investigated theorem prover based verifications of SRT division hardware. Clarke, German, and Zhao used the ANALYTICA theorem prover to verify Taylor's [Tay81] radix-4 SRT division circuit [CGZ96]. Their verification includes an abstract representation of the lookup table and a proof that it defines all necessary values for the quotient selection logic. Rueß, Srivas, and Shankar [RSS96] generalize this work using PVS. They present a general verification of arbitrary radix SRT division algorithms, instantiate their theory with Taylor's radix-4 SRT division circuit, and verify a description of the hardware. Included in their work is a technique to verify a concrete representation of the lookup table. Miner and Leathrum provide a further generalization to the class of subtractive division algorithms and relate this class of algorithms to a floating-point standard [ML96]. This

provides the entry point for the derivation activities presented in Chapter 6. Recently, the microcode for the floating point division and square root algorithms of the  $AMD5_K86^{TM}$  microprocessor has been mechanically verified using the ACL2 theorem prover [BKM96].

Within a general purpose theorem proving system, there are several ways to represent hardware artifacts. One of the most common is the relational style advocated by Gordon [Gor86]. Signals are represented as functions from discrete points in time to the signal type. Circuit components are defined as relations between signals; hardware structure is defined by relation composition. Bronstein and Talcott present a string-functional semantics for reasoning about hardware using nqthm [BT90]. This supports describing hardware structure using a functional style similar to that used in DRS. Paulin-Mohring has used a coinductive representation of streams in CoQ to explore their application in hardware verification [Pau95]. She illustrated the approach using Gordon's multiplier circuit [Gor86]. She did not explore use of bisimulations for showing circuit equivalence, but suggested it as an interesting possibility. Coupet-Grimal and Jakubiec have exploited the constructive nature of CoQ to extract circuits from proofs [CJ96]. In particular, they follow the example of Hanna, Daeche, and Longley's VERITAS+ system [HDL89] and use dependent types to construct parameterized circuit modules.

#### Algebraic Approaches

A number of algebraic approaches have been proposed for formal reasoning about digital hardware design. In addition to the design derivation tools discussed above, there is the Ruby design algebra [She88] and the work of Harman and Tucker [HT96]

Harman and Tucker present an algebraic model of synchronous digital hardware. The general hardware representation is by iterated maps. Let T represent time, A be set of states, W be a set of input values,  $[T \to W]$  be a set of input streams, and X be a set of output values. A sequential system is modeled by function  $F: T \times A \times [T \to W] \to A \times X$ , where:

$$F_1(0, a, w) = a.$$

$F_1(t+1, a, w) = next\_state(F_1(t, a, w), w(t)),$

$F_2(t, a, w) = out(F_1(t, a, w)).$

When the set of states A is finite, this is a description of a Moore machine [Moo56]. It provides a rigorous mathematical description of synchronous hardware, and lends itself to inductive verification. However, this representation has the complication that the current state is represented as a function of the initial state and past history of the input stream. Frequently, the initial state of a hardware device is irrelevant. Also, the current state of a device only depends upon a limited past history of the input stream. My experiences in proving hardware using this representation is that it distracts from the main verification goal. This structure is similar to that used in the PVS proofs of the clock synchronization circuit presented in [MPJ94]. In that verification effort, more time was spent dealing with quirks of the model than in verifying the refinement. The verification presented in [MPJ94] has been redone using coinduction and is presented in Chapter 5.

Ruby is a relational algebra for digital hardware design. Circuit components are defined as relations between signals; systems are built up via relational composition. The primary difference with other representations is that time is infinite in both directions, eliminating the distraction of an irrelevant initial state. The language was introduced by Jones and Sheeran [JS90], and is particularly well suited to refining

circuits with a regular structure. The Ruby design philosophy is similar to the underlying design philosophy for DRS, in that it supports a transformational approach to circuit design. It has been demonstrated on a number of circuit designs, including a pipelined systolic correlator [She88]. Recently, Sharp and Rasmussen developed a strongly typed version called T-Ruby [SR97]. It is based upon Pure Ruby [Ros90], which consists of four basic constructs. In T-Ruby, all circuits and combinators are built up from the pure core. Rasmussen has developed a proof system called RubyZF using the Isabelle theorem prover [Ras96]. RubyZF enables mechanical verification of all T-Ruby transformations, and provides integrated reasoning support for verifying proof obligations generated by T-Ruby.

The synchronous data-flow language LUSTRE has been used effectively in the design and verification of synchronous hardware [HCRP91, TP90]. The language was originally developed for the specification and verification of real-time systems and was inspired by the dataflow language Lucid [WA85]. Lustre is a declarative language where expressions represent sequences of values. Systems are specified using a collection of equations. The verification tool Lesar provides a state exploration technique similar to model checking.

#### 2.4 Coinduction and Corecursion

This dissertation does not address foundational issues of coinduction or corecursion, but rather focuses on a specific application. There are a number of foundational treatments in the literature. One such basis is Aczel's Special Final Coalgebra Theorem [Acz88]. Another is Barwise and Moss' Corecursion Theorem [BM96]. Recently, Moss and Danner have further explored foundational issues and have suggested that

corecursion may by justified by reduction to recursion [MD97]. Research in constructive type theory has also addressed the notion of types of infinite objects. The first treatments were by Mendler et al. [MPC86, Men87], with subsequent investigations by Coquand [Coq93] and Leclerc and Paulin-Mohring [LP93].

Applications of coinduction to verification have their root in process calculi such as CCS [Mil89]. Park appears to be among the first to explore the use of greatest fixed points as a verification strategy [Par80, Par81]. Other applications include programming language semantics [MT91, Pit94]. Giménez used coinductive types in CoQ for the verification of an alternating bit protocol [Gim95]. Recently, Jacobs has explored coinductive verification techniques for class refinement in an object-oriented setting [Jac97].

There have been a number of recent efforts seeking to provide mechanized reasoning support for coinductive verification techniques. Paulson built up a framework for inductive and coinductive datatypes in Isabelle-HOL [Pau97]. Inductive types are expressed as least fixed points and coinductive types are expressed as greatest fixed points. Leclerc and Paulin-Mohring have explored coinductive types using the CoQ system [LP93]. Recently, Hensel and Jacobs have provided mechanized support for coinductive reasoning in PVS by developing a theory of final coalgebras [HJ97a, HJ97b].

## Reasoning about Streams

Many approaches to formal verification of hardware represent signals as streams, i.e. functions from time to value, where time ranges over the natural numbers. These previous verification activities have not exploited the fact that streams are a coinductively generated type and hence also allow proof by coinduction. This chapter introduces some basic properties of streams, and illustrates the use of the mechanized reasoning system PVS to reason about them.

#### 3.1 Stream Basics

A stream over A is an infinite sequence

$$x = [x_0, x_1, x_2, \ldots]$$

where each  $x_i \in A$ . The constructor cs adds an element to the front of the sequence. Take  $a \in A$  and x as above, then

$$cs(a, x) = [a, x_0, x_1, x_2, \ldots]$$

The natural model for streams over A is  $\mathbb{N} \to A$ , with the following definition for cs:

$$cs(a,x)(n) = \begin{cases} a & \text{if } n = 0\\ x(n-1) & \text{otherwise} \end{cases}$$

Streams may also be viewed coinductively, that is, as a greatest fixed-point of a monotone operator. An operator  $F: \mathcal{P}(\mathcal{U}) \to \mathcal{P}(\mathcal{U})$  is monotone if  $F(X) \subseteq F(Y)$  whenever  $X \subseteq Y$ . The greatest fixed-point of monotone F, defined by

$$\nu Z.F(Z) = \bigcup \{Z | Z \subseteq F(Z)\}$$

is the largest set Z such that Z = F(Z).

Fix a class  $\mathcal{U}$  and  $\operatorname{cs}: A \times \mathcal{U} \to \mathcal{U}$  for some set A. Define monotone operator  $\operatorname{CS}_A: \mathcal{P}(\mathcal{U}) \to \mathcal{P}(\mathcal{U})$  by

$$\mathsf{CS}_A(X) = \{\mathsf{cs}(a,x) | a \in A \ \& \ x \in X\}$$

The set  $A^{\infty}$  of streams over A is defined as the greatest fixed-point of  $\mathsf{CS}_A$ .

$$A^{\infty} \triangleq \nu Z.\mathsf{CS}_A(Z)$$

$$= \{\mathsf{cs}(a,x) | a \in A \& x \in A^{\infty} \}$$

The constructor **cs** and universe  $\mathcal{U}$  must be selected so that whenever  $A \neq \emptyset$  then also  $A^{\infty} \neq \emptyset$  and furthermore, there exist functions  $\mathsf{hd}: A^{\infty} \to A$  and  $\mathsf{tl}: A^{\infty} \to A^{\infty}$

so that for  $a \in A$  and  $x \in A^{\infty}$ :

$$hd(cs(a,x)) = a$$

$$tl(cs(a,x)) = x$$

$$cs(hd(x),tl(x)) = x$$

Using the standard model of streams, that is, setting  $\mathcal{U} = \mathbf{N} \to A$ , defining cs as above, and defining  $\mathsf{hd}(x) = x(0)$  and  $\mathsf{tl}(x) = \lambda n.x(n+1)$ , these equations are easily verified. An elegant model of streams is found in the universe of non-well-founded sets, where it is possible to define  $\mathsf{cs}(a,x) = \langle a,x \rangle$  [BM96].

A trivial consequence of the fact that  $A^{\infty} = \bigcup \{Z | Z \subseteq \mathsf{CS}_A(Z)\}$  is the following proof principle:

Coinduction Principle: To show that  $x \in A^{\infty}$ , exhibit a Z such that  $x \in Z$  and  $Z \subseteq \mathsf{CS}_A(Z)$ .

We use the coinduction principle to build towards a general mechanism for defining streams.

**Theorem 1** For  $g: A \rightarrow A$  and  $a \in A$ , if

$$\mathsf{iter}_g(a) = \mathsf{cs}(a,\mathsf{iter}_g(g(a))) \tag{3.1}$$

$then\ \mathsf{iter}_g(a) \in A^\infty$

**Proof:** Let

$$Z = \{\mathsf{iter}_g(a) \mid a \in A\}$$

We need to show that  $Z \subseteq \mathsf{CS}_A(Z)$ . Given  $a' \in A$ ,  $\mathsf{iter}_g(a') \in Z$ . From equation (3.1),  $\mathsf{iter}_g(a') = \mathsf{cs}(a', \mathsf{iter}_g(g(a')))$ . Since  $a' \in A$  and  $\mathsf{iter}_g(g(a')) \in Z$ , we have  $\mathsf{iter}_g(a') \in \mathsf{CS}_A(Z)$ . Since the choice of a' was arbitrary,  $Z \subseteq \mathsf{CS}_A(Z)$ .

Since for any  $a \in A$ ,  $\operatorname{iter}_g(a) \in Z$  and  $Z \subseteq \mathsf{CS}_A(Z)$ , we use the coinduction principle to conclude  $\operatorname{iter}_g(a) \in A^{\infty}$ .

The next question is whether a solution to equation 3.1 is unique. This requires a principle of equality. Two streams are equal if and only if they are indistinguishable at every finitely accessible point. The following proof principle provides a useful tool for demonstrating equality between streams.

**Definition** A stream bisimulation is a relation R between  $A^{\infty}$  and  $A^{\infty}$  so that whenever s R t, then

$$hd(s) = hd(t)$$

and  $tl(s) R tl(t)$

Coinduction principle If  $x, y \in A^{\infty}$  and x R y for some bisimulation R, then x = y.

A proof of this principle in the universe of non-well-founded sets is on page 84 of [BM96]. Jacobs and Rutten use the fact that streams are a final coalgebra to justify this principle [JR97]. Here we directly show that two streams in a stream bisimulation are indistinguishable.

**Theorem 2** For  $n \in \mathbb{N}$  if  $x, y \in A^{\infty}$  and x R y for some bisimulation R, then  $hd(t|^n(x)) = hd(t|^n(y))$ .

**Proof:** By induction on n.

**Base case:** Since R is a bisimulation and x R y, we have

$$\mathsf{hd}(\mathsf{tl}^0(x)) = \mathsf{hd}(x) = \mathsf{hd}(y) = \mathsf{hd}(\mathsf{tl}^0(y))$$

Induction step: The induction hypothesis asserts that if  $x', y' \in A^{\infty}$  and x' R y' then  $\mathsf{hd}(\mathsf{tl}^n(x')) = \mathsf{hd}(\mathsf{tl}^n(y'))$ . Since R is a bisimulation and x R y, we have  $\mathsf{tl}(x) R \mathsf{tl}(y)$ . Using the induction hypothesis, we get  $\mathsf{hd}(\mathsf{tl}^n(\mathsf{tl}(x))) = \mathsf{hd}(\mathsf{tl}^n(\mathsf{tl}(y)))$ . Simplification yields  $\mathsf{hd}(\mathsf{tl}^{n+1}(x)) = \mathsf{hd}(\mathsf{tl}^{n+1}(y))$

Corollary 1 For any stream bisimulation R,

$$R \subseteq \{(x,y)|\forall (n \in \mathbf{N}).\mathsf{hd}(\mathsf{tl}^n(x)) = \mathsf{hd}(\mathsf{tl}^n(y))\}$$

If we define a monotone operator on  $\mathcal{U} = A^{\infty} \times A^{\infty}$  by:

$$F(R) = \{(x,y)|\mathsf{hd}(x) = \mathsf{hd}(y) \text{ and } \mathsf{tl}(x) \ R \ \mathsf{tl}(y)\}$$

then

$$\nu R.F(R) = \{(x,y) | \forall (n \in \mathbf{N}).\mathsf{hd}(\mathsf{tl}^n(x)) = \mathsf{hd}(\mathsf{tl}^n(y)) \}$$

Now we can use the coinduction principle to show that equation 3.1 has a unique solution.

**Theorem 3** Suppose I(a) = cs(a, I(g(a))), then  $I(a) = iter_g(a)$

**Proof:** By coinduction using relation

$$R=\{(I(a),\, \mathrm{iter}_g(a))|a\in A\}$$

It is clear that I(a) R iter<sub>g</sub>(a) for all  $a \in A$ . All that remains is to show that R is a stream bisimulation.

Take  $x, y \in A^{\infty}$  such that  $x \in R$  y. That is, there is an  $a \in A$  such that x = I(a) and  $y = iter_a(a)$ . There are two properties to be shown

1.

$$hd(x) = hd(I(a)) = a = hd(iter_g(a)) = hd(y)$$

2. Using equations (3.1) and the hypothesis above, we conclude that

$$\mathsf{tl}(x) = \mathsf{tl}(I(a)) = \mathsf{tl}(\mathsf{cs}(a, I(g(a)))) = I(g(a))$$

and

$$\mathsf{tl}(y) = \mathsf{tl}(\mathsf{iter}_q(a)) = \mathsf{tl}(\mathsf{cs}(a,\mathsf{iter}_q(g(a)))) = \mathsf{iter}_q(g(a))$$

Since

$$g(a) \in A$$

,  $\mathsf{tl}(x) \ R \ \mathsf{tl}(y)$ .

Thus, equation (3.1) uniquely determines a stream for each  $a \in A$  and any function  $g: A \to A$ . Iter provides a mechanism for defining several streams over A. The next requirement is a functional to map a function  $f: A \to B$  to every element of a stream over A.

Theorem 4 For  $s \in A^{\infty}$  and  $f: A \rightarrow B$ , if

$$\mathsf{map}_f(s) = \mathsf{cs}(f(\mathsf{hd}(s)), \mathsf{map}_f(\mathsf{tl}(s))) \tag{3.2}$$

$then \ \mathrm{map}_f(s) \in B^{\infty}.$

**Proof:** Let

$$Z = \{ \max_f(s) | s \in A^{\infty} \}$$

We need to show that  $Z \subseteq \mathsf{CS}_B(Z)$ . Given any  $s \in A^\infty$ ,  $\mathsf{map}_f(s) \in Z$ . We know that since  $s \in A^\infty$  there are  $a \in A$  and  $s' \in A^\infty$  such that  $s = \mathsf{cs}(a, s')$ . By the definition of  $\mathsf{map}$  we have  $\mathsf{map}_f(s) = \mathsf{cs}(f(a), \mathsf{map}_f(s'))$ . This is an element of  $\mathsf{CS}_B(Z)$ , so  $Z \subseteq \mathsf{CS}_B(Z)$ .

Since  $\operatorname{\mathsf{map}}_f(s) \in Z$  and  $Z \subseteq \operatorname{\mathsf{CS}}_B(Z)$ , we use the coinduction principle to conclude  $\operatorname{\mathsf{map}}_f(s) \in B^\infty$ .

A coinductive proof suffices to show that map is unique.

**Theorem 5** For  $s \in A^{\infty}$ , given  $f: A \to B$ , if  $m: A^{\infty} \to B^{\infty}$  satisfies

$$m(s) = \operatorname{cs}(f(\operatorname{hd}(s)), m(\operatorname{tl}(s)))$$

$then \ m(s) = \mathsf{map}_f(s)$

**Proof:** By coinduction using relation

$$R=\{(m(s),\; \mathrm{map}_f(s))|s\in A^\infty\}$$

It is clear that m(s) R  $\mathsf{map}_f(s)$  for all  $s \in A^{\infty}$ . All that remains is to show that R is a stream bisimulation.

Take  $x, y \in A^{\infty}$  such that x R y. That is, there is an  $s \in A^{\infty}$  such that x = m(s) and  $y = \mathsf{map}_f(s)$ . There are two properties to be shown

1.

$$hd(x) = hd(m(s)) = f(hd(s)) = hd(map_f(s)) = hd(y)$$

2. Using equations (3.2) and the hypothesis above, we conclude that

$$\mathsf{tl}(x) = \mathsf{tl}(m(s)) = \mathsf{tl}(\mathsf{cs}(f(\mathsf{hd}(s)), m(\mathsf{tl}(s)))) = m(\mathsf{tl}(s))$$

and

$$\label{eq:tl} \begin{split} \mathsf{tl}(y) &= \mathsf{tl}(\mathsf{map}_f(s)) = \mathsf{tl}(\mathsf{cs}(f(\mathsf{hd}(s)), \mathsf{map}_f(\mathsf{tl}(s)))) = \mathsf{map}_f(\mathsf{tl}(s)) \\ \\ \mathrm{Since} \ \mathsf{tl}(s) &\in A^\infty, \ \mathsf{tl}(x) \ R \ \mathsf{tl}(y). \end{split}$$

Given  $f: A \to B$ ,  $g: A \to A$ . Consider the function  $\mathsf{corec}_{(f,g)}: A \to B^{\infty}$  defined by

$$\mathsf{corec}_{(f,g)}(a) \; \stackrel{\triangle}{=} \; \mathsf{map}_f(\mathsf{iter}_g(a)) \tag{3.3}$$

This function provides a useful tool for providing solutions to corecursive stream equations.

## Theorem 6

$$\operatorname{corec}_{(f,g)}(a) = \operatorname{cs}(f(a), \operatorname{corec}_{(f,g)}(g(a))) \tag{3.4}$$

Proof:

$$\begin{aligned} \mathsf{corec}_{(f,g)}(a) &= \mathsf{map}_f(\mathsf{iter}_g(a)) & ; \text{ by equation } (3.3) \\ &= \mathsf{map}_f(\mathsf{cs}(a,\mathsf{iter}_g(g(a)))) & ; \text{ by equation } (3.1) \\ &= \mathsf{cs}(f(a),\mathsf{map}_f(\mathsf{iter}_g(g(a)))) & ; \text{ by equation } (3.2) \\ &= \mathsf{cs}(f(a),\mathsf{corec}_{(f,g)}(g(a))) & ; \text{ by equation } (3.3) \end{aligned}$$

$\dashv$

Suppose we want to find a solution for  $c_a$  in the equation:

$$c_a = \mathsf{cs}(a, c_a) \tag{3.5}$$

We can use **corec**. Assume that A = B, then define

$$c_a \triangleq \mathsf{corec}_{(id_A, id_A)}(a) \tag{3.6}$$

Lemma 1  $c_a = cs(a, c_a)$

**Proof:**

$$c_a = \operatorname{corec}_{(id_A,id_A)}(a)$$

; by equation (3.6)

$= \operatorname{cs}(id_A(a),\operatorname{corec}_{(id_A,id_A)}(id_A(a)))$  ; by equation (3.4)

$= \operatorname{cs}(a,\operatorname{corec}_{(id_A,id_A)}(a))$  ; definition of  $id_A$

$= \operatorname{cs}(a,c_a)$  ; by equation (3.6)

Corec may be used to define a solution to equation 3.1

Fact 1

$$iter_g(a) = corec_{(id,g)}(a)$$

**Proof:** By coinduction, using bisimulation

$$\{(\mathsf{iter}_g(a), \mathsf{corec}_{(id,g)}(a)) | a \in A\}.$$

Inspection of the above bisimulation shows that it is defined in a simple manner from the equality to be proven. When a bisimulation is of this form, it is trivial to show that the streams being shown equal are in the relation. This technique for constructing bisimulations is quite common in coinductive proofs. A bisimulation constructed in

$\dashv$

this manner is a *trivial bisimulation*. The proof steps are mechanical and can be automated.

As an additional example of verifying stream equivalence using coinduction, consider the following identity. This is frequently given as an alternative definition for iter.

#### Fact 2

$$iter_g(a) = cs(a, map_g(iter_g(a)))$$

(3.7)

**Proof:** By coinduction using bisimulation  $\{(\mathsf{iter}_g(a), \mathsf{cs}(a, \mathsf{map}_g(\mathsf{iter}_g(a)))) | a \in A\} \ \exists$

Barwise & Moss introduce a few other stream equations and some exercises for practicing coinductive proofs. These will be used as illustrative test cases for the PVS streams theories presented in the next section. The definitions and identities are:

$$\mathsf{map}_f(c_a) = c_{f(a)} \tag{3.8}$$

$$\mathsf{zip}(\mathsf{cs}(a,s),\mathsf{cs}(b,t)) \ \hat{=} \ \mathsf{cs}(a,\mathsf{cs}(b,\mathsf{zip}(s,t))) \tag{3.9}$$

$$\mathsf{zip}(c_a, c_a) = c_a \tag{3.10}$$

$$iter_f(a) = zip(iter_{f \circ f}(a), map_f(iter_{f \circ f}(a)))$$

(3.11)

$$\mathsf{dmap}_f(s) \ \hat{=} \ \mathsf{cs}(f(\mathsf{hd}(s)), \mathsf{dmap}_f(\mathsf{dmap}_f(\mathsf{tl}(s)))) \tag{3.12}$$

recalling that  $iter_g(a)$ ,  $map_f(s)$ , and  $c_a$  satisfy equations (3.1), (3.2), and (3.5), respectively.

3. Reasoning about Streams

33

Defining Streams in PVS 3.2

Developing support for mechanized reasoning about streams is complicated by

the fact that it must be developed within the logic of some mechanized proof system.

Traditionally, streams over A have been represented by  $[N \to A]$ . The initial efforts

to reason about streams in PVS [MPJ94] used this representation. However, this

choice of representation led to emphasis on proofs by induction, even though we were

modeling objects that were defined (within DDD) using stream equations. As shown

in the previous section, corecursive stream equations naturally lead to proofs using

coinduction.

The PVS streams library is modeled after the PVS abstract datatype mecha-

nism [OS93]. The principal definition of the stream codatatype is parameterized by

nonempty type  $\alpha$ . The type of streams over  $\alpha$  is defined as an uninterpreted nonempty

type. As in the PVS abstract datatype mechanism, the type is constrained by axioms

about uninterpreted constructor and accessor functions. The PVS abstract datatype

mechanism supports recursive function definition and proofs by induction. Similarly,

the streams library provides support for corecursive function definition and proofs by

coinduction. The streams library is available electronically [WWW].

The following initial fragment from PVS theory Stream\_cdt provides the declara-

tion of type Stream[alpha], and defines the type signature for Stream constructor cs

and accessors hd and tl.

Stream\_cdt[alpha: TYPE+]: THEORY

BEGIN

Stream: TYPE+

cs: [alpha, Stream -> Stream]

hd: [Stream -> alpha]

#### tl: [Stream -> Stream]

The constructor cs and accessors hd and tl are constrained by the usual axioms. In the following axioms, S has type Stream[alpha] and a has type alpha.

$Stream_cs_eta : AXIOM cs(hd(S), tl(S)) = S$

$hd_cs$  : AXIOM hd(cs(a, S)) = a

$tl_cs$  : AXIOM tl(cs(a, S)) = S

Since type Stream is uninterpreted, there is no general mechanism in PVS for proving equality between streams. We need to introduce an axiom that defines what we mean by stream equality. Axiom Stream\_eq defines two streams be equal if and only if they are indistinguishable at every finitely accessible point.

Function iterate, used in the definition of function nth, is defined in the PVS prelude. For any type T, x : T, and function  $g : T \to T$ ,

$$iterate(g,n)(x) = g^n(x).$$

Thus, function nth returns the  $n^{th}$  element of a stream.

The final base definition for the PVS Streams library is the corecursion combinator:

$$corec: ((\alpha \to \beta) \times (\alpha \to \alpha)) \to (\alpha \to \beta^{\infty})$$

Given  $f: \alpha \to \beta$ ,  $g: \alpha \to \alpha$  and  $a: \alpha$ , we axiomatize the behavior of the corecursion combinator via the following PVS declaration:

```

corec_def: AXIOM corec(f, g)(a) = cs(f(a), corec(f, g)(g(a)))

```

Given this definition, and the previous axioms, we prove the following two facts. The proofs consist of rewriting with corec\_def and then rewriting with either hd\_cs or tl\_cs.

```

hd_corec: FACT

hd(corec(f, g)(a)) = f(a)

tl_corec: FACT

tl(corec(f, g)(a)) = corec(f, g)(g(a))

```

For each function  $F: \alpha \to \beta^{\infty}$  that is defined using corec, I adopt the convention that the following three facts are also introduced and proven within PVS:

```

F_def: FACT

F(a) = cs(f(a),F(g(a)))

hd_F: FACT

hd(F(a)) = f(a)

tl_F: FACT

tl(F(a)) = F(g(a))

```

These proof obligations are easily discharged. With the exception of F\_def, no theorems about F are proven directly from the corecursive definition. Establishing these three facts about streams defined using corec greatly simplifies subsequent coinductive proofs.

The functions f and g used in corecursive definitions are often complicated. If we allow function definitions using corec to be expanded by some of the powerful proof strategies within PVS, it is possible that much of the proof time could be consumed by trivial details. Thus, we desire some mechanism to hide the corecursion combinator from the standard automatic proof strategies within PVS. The following definitional scheme suffices:

```

F(a): \{B : Stream[beta] \mid B = corec(f, g)(a)\}

```

This style of definition exploits the PVS dependent type mechanism. In this declaration, function  $F: \alpha \to \beta^{\infty}$  is both uninterpreted and completely defined. Since there is no body, the function cannot be expanded or rewritten. The only access to the definition of this function is via the PVS proof command (typepred "F(a)"), for some a:alpha. The equation F\_def is proven using the typepred command followed by rewriting with corec\_def.

As an illustration of this template, here is the corecursive definition of map:

Facts hd\_map and tl\_map are trivial consequences of map\_def, hd\_cs, and tl\_cs. The

only remaining obligation is the proof of map\_def. It follows from the dependent type constraints and corec\_def.

The proofs justifying definition by corecursion have the same structure. To simplify the handling of these proof obligations, I have defined a PVS strategy to discharge goals of this form. Consider the corecursive definition of iter:

```

iter((g : [alpha -> alpha]), (a :alpha)) :

{ A : Stream[alpha] | A = corec(id[alpha], g)(a)}

iter_def : FACT

iter(g, a) = cs(a, iter(g, g(a)))

```

The PVS justification of iter\_def uses the proof strategy (def-corec):

**Proof:** (Taken verbatim from the \*pvs\* proof buffer)

In addition, we define the appropriate supporting facts concerning the head and tail of iter.

```

hd_iter : FACT

hd(iter(g, a)) = a

tl_iter : FACT

tl(iter(g, a)) = iter(g, g(a))

```

These facts are also simply discharged within PVS. This template is followed for all stream definitions within the PVS streams library.

For a more complicated example of stream definition using the corecursion combinator, consider equation (3.9) from section 3.1. The challenge (from Barwise and Moss [BM96]) is to show that there is a function  $zip:A^{\infty} \times A^{\infty} \to A^{\infty}$  that satisfies the equation:

```

zip(X,Y) = cs(hd(X), cs(hd(Y), zip(tl(X), tl(Y))))

```

At first glance, it does not appear that zip can be defined using corec. However, one of the laws for zip is

```

zip(X,Y) = cs(hd(X), zip(Y, tl(X)))

```

This leads us to a correct definition of zip using corec

```

zip(X,Y): \{Z \mid Z = corec(lambda X,Y: hd(X), lambda X,Y: (Y,tl(X)))(X,Y)\}

```

From this, we easily establish that zip satisfies equation (3.9).

# Proof of stream equality using coinduction

Using axiom Stream\_eq (page 34), we can prove stream equality using function nth and induction. However, section 3.1 demonstrated proofs of stream equality using the coinduction principle.

The PVS definition of the coinduction principle for proving stream equality is given in theorem co\_induct below:

```

Bisimulation: TYPE =

{R : PRED[[Stream[alpha], Stream[alpha]]] |

FORALL X, Y:

R(X, Y) =>

hd(X) = hd(Y) & R(tl(X), tl(Y))}

co_induct: THEOREM

(EXISTS (R: Bisimulation): R(X, Y)) => X = Y

```

Theorem co\_induct is a trivial consequence of Axiom Stream\_eq and Theorem 2. It has be proven using PVS. The PVS theories are available electronically [WWW].

## **Invariants on Streams**

Proof by coinduction is also used to establish invariant properties of a stream. Relations are lifted to streams, yielding streams over the booleans. As an example, suppose we are given two boolean streams A and B. We lift implication to these streams yielding a boolean valued stream satisfying the equation

```

(A \Rightarrow B) = cs(hd(A) \Rightarrow hd(B), tl(A) \Rightarrow tl(B))

```

In this example, the symbol '=>' is overloaded. In sub-term hd(A) => hd(B) it has (PVS) type [bool, bool -> bool] and has type [Stream[bool], Stream[bool] -> Stream[bool]] in the other occurrences.

One way to make the assertion that  $\forall n : n^{th}(A, n) \Rightarrow n^{th}(B, n)$  is to identify stream (A => B) with stream const(true). If this identity is true, it is easily proven using the coinduction principle for showing stream equality. This identification is sufficiently useful that we have defined the abbreviation:

```

Invariant(A : Stream[bool]) : bool = (A = const(true))

```

With this construct we define a coinduction principle for verifying that streams satisfy invariant properties.

```

CoInductive_Assertion: TYPE =

{ (P : PRED[Stream[bool]]) |

FORALL A: P(A) => hd(A) & P(tl(A)) }

co_induct: THEOREM

(EXISTS (P : CoInductive_Assertion): P(A)) => Invariant(A)

```

This is a simple consequence of the coinduction principle for stream equality. Alternatively, one could define:

```

Invariant(A : Stream[bool]) : bool = FORALL (n:nat): nth(A,n)

```

and then prove this coinduction principle using the same proof structure as shown for the coinduction principle for stream equality.

# Coinductive Proofs using PVS

In this section we revisit some of the stream equations given in section 3.1 and illustrate approaches for coinductive proofs using PVS. First, consider equation (3.7).

```

Fact 3 iter(g, a) = cs(a, map(g, iter(g, a)))

```

**Proof:** The initial PVS step strips off the universal quantifiers.

```

iter_map_def :

|-----

{1}     (FORALL (a: alpha, g: [alpha -> alpha]):

iter(g, a) = cs(a, map(g, iter(g, a))))

Rule? (SKOLEM!)

Skolemizing,

```

this yields 2 subgoals:

Y = cs(a, map(g!1, iter(g!1, a)))")

The first subgoal is to show that the two streams are in the provided relation, the second is to show that the relation is a bisimulation. After beta reduction, the first subgoal simplifies to

The (inst?) command asks PVS to guess a value to provide for the existentially quantified variable. In this case, PVS correctly guesses a!1, resulting in a goal that is easily proven using propositional simplification.

The second subgoal is to show that the given relation is a bisimulation. After the proof steps (skosimp\*)(replace\*)(hide -1 -2) the resulting goal is:

This splits into the two standard cases for showing that a relation is a bisimulation. The first subgoal is to prove that the heads are equal

```

Rule? (split)

Splitting conjunctions,

this yields 2 subgoals:

```

$\dashv$

Rewriting with hd\_cs and hd\_iter discharges this goal. Leaving us with:

```

iter_map_def.2.2 :

```

In this branch, we rewrite with map\_def, tl\_cs, hd\_iter, and tl\_iter giving us the following goal:

```

{1} EXISTS (a: alpha):

iter(g!1, g!1(a!2)) = iter(g!1, a)

& cs(g!1(a!2), map(g!1, iter(g!1, g!1(a!2))))

= cs(a, map(g!1, iter(g!1, a)))

```

The commands (inst?) and (prop) finish off the proof.

Most of the steps in the proof given above are common to many coinductive proofs. I have defined a PVS strategy named co-induct that handles some of the routine aspects of a coinductive proof. In particular, it automatically discharges the membership subgoal when presented with a trivial bisimulation. In addition, it reduces the proof obligation that the given relation is a bisimulation into the two standard subgoals: the heads are equal, and the tails are in the relation.

The following PVS proof proof of equation (3.8) illustrates the (co-induct) strategy.

```

Fact 4 map(f,const(a)) = const(f(a))

```

#### **Proof:**

```

map_const :

{1}

(FORALL (a: alpha, f: [alpha -> beta]):

map(f, const(a)) = const(f(a)))

Rule? (CO-INDUCT

"{(X,Y:Stream[beta]) |

EXISTS f, a:

X=map(f,const(a)) &

Y=const(f(a))}")

this yields 2 subgoals:

map_const.1 :

hd(map(f!2, const(a!2)))

{1}

= hd(const(f!2(a!2)))

Rule? (postpone)

Postponing map_const.1.

map_const.2 :

{1}

EXISTS (f: [alpha -> beta]), (a: alpha):

tl(map(f!2, const(a!2)))

= map(f, const(a))

& tl(const(f!2(a!2))) = const(f(a))

```

Rule?

The first subgoal is proven by rewriting with hd\_map and hd\_const. The second subgoal is proven by rewriting with tl\_map and tl\_const, followed by (inst?) and (assert).

The information necessary to construct a trivial bisimulation is present in the initial goal. PVS provides some lisp functions that help in collecting information from formulae in the sequent and in generating terms for use in later proof steps. Using these, I developed a more advanced PVS strategy named simple-co-induct that automatically generates a candidate bisimulation and then invokes strategy co-induct. Consider equation (3.10) from section 3.1.

```

Fact 5 zip(const(a),const(a)) = const(a)

```

**Proof:** The following sequence of commands suffice to prove equation (3.10) using PVS and the streams library.

$\dashv$

Coinductive proofs are automated further. Recall that the template for introducing corecursive stream definitions includes two facts for simplifying the head and tail of a given stream. These are installed as automatic rewrites and combined with some of the existing brute force strategies within PVS to provide powerful strategies for determining coinductive proofs using PVS. The most potent strategy for discovering coinductive proofs is co-induct-and-simplify. It is sufficiently powerful to prove

the preceding equations automatically. The following PVS proof of equation (3.3) demonstrates the utility of strategy (co-induct-and-simplify)

```

Fact 6 corec(f,g)(a) = map(f,iter(g,a))

```

```

Rule? (CO-INDUCT-AND-SIMPLIFY)

hd_corec rewrites hd(corec(f!2, g!2)(a!2))

to f!2(a!2)

hd_iter rewrites hd(iter(g!2, a!2))

to a!2

hd_map rewrites hd(map(f!2, iter(g!2, a!2)))

to f!2(a!2)

tl_corec rewrites tl(corec(f!2, g!2)(a!2))

to corec(f!2, g!2)(g!2(a!2))

tl_iter rewrites tl(iter(g!2, a!2))

to iter(g!2, g!2(a!2))

tl_map rewrites tl(map(f!2, iter(g!2, a!2)))

to map(f!2, iter(g!2, g!2(a!2)))

```

Showing equivalence by exhibiting trivial bisimulation,  $\ensuremath{\mathbb{Q}}.E.\,D.$

The strategy co-induct-and-simplify is also useful for establishing equations (3.11) and (3.12). To prove equation (3.11), we first introduce the following lemma.

```

Lemma 2 map(f,iter(f o f,a)) = iter(f o f,f(a))

```

**Proof:** Using PVS strategy co-induct-and-simplify.

$\dashv$

```

Fact 7 iter(f,a) = zip(iter(f o f,a),map(f,iter(f o f,a)))

```

**Proof:** Strategy (co-induct-and-simplify) leaves us with the goal:

|----

Rewriting twice with lemma 2 and once with "o" completes the proof.

The challenge of equation (3.12) is to prove that such a function exists. Define F(f,S) = f(hd(S)) and  $G(f,S) = (f \circ f, tl(S))$ , then define

```

dmap(f,S): \{ S1 \mid S1 = corec(F,G)(f,S) \}

```

From this corecursive definition, it is trivial to establish

```

dmap_def: LEMMA

dmap(f,S) = cs(f(hd(S)),dmap(f o f,tl(S)))

hd_dmap : LEMMA

hd(dmap(f,S)) = f(hd(S))

tl_dmap : LEMMA

tl(dmap(f,S)) = dmap(f o f,tl(S))

```

All that remains is to show that this function dmap defines a stream that satisfies equation (3.12).

```

Fact 8 dmap(f,S) = cs(f(hd(S)), dmap(f, dmap(f,t1(S))))

```

**Proof:** Using (co-induct-and-simplify) we get the following goal:

Rewriting with dmap\_def and "o" completes the proof.

## Advanced examples of stream definition

Thus far, the streams we have examined had a very simple form. In the study of streams there are some more complicated examples. This section presents corecursive definitions for two: filter and sharp.