# TECHNICAL REPORT NO. 339

Area-Efficient Implication Circuits for Very Dense Łukasiewicz Logic Arrays

by

Jonathan W. Mills

November 1991

COMPUTER SCIENCE DEPARTMENT

INDIANA UNIVERSITY

Bloomington, Indiana 47405-4101

## Area-Efficient Implication Circuits for Very Dense Łukasiewicz Logic Arrays

Jonathan W. Mills\* Indiana University Bloomington, Indiana 47405

## Abstract

A one-diode circuit for negated implication (\$\pi\$) is derived from a 12-transistor £ukasiewicz implication circuit (\$\pi\$). The derivation also yields an adjustable three-transistor implication circuit with maximum error less than 1% of full scale. Two £ukasiewicz logic arrays (£LAs) are proposed that use area-efficient implementations of the one-diode and three-transistor implication circuits. The very dense diode-tower £LA contains 36,000 implications in an area that previously held 92 implications; the three-transistor £LA contains 1,990 implications. Both £LAs double the number of inputs per pin on the IC package. Very dense £LAs make £LA-based fuzzy controllers and neural networks practical.

#### 1. INTRODUCTION

## 1.1 ŁUKASIEWICZ LOGIC AND ELECTRONIC CIRCUITS

Continuous-valued analog circuits for Łukasiewicz implication ( $\supset$ ) and negated implication ( $\updownarrow$ ) are the basis for analog array processors called Łukasiewicz logic arrays (£LAs) [1].

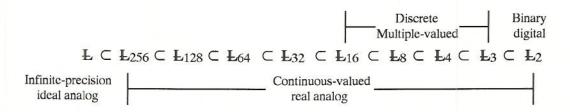

Łukasiewicz logic ( $\mathbb{L}$ ) has a denumerably infinite number of truth values [2].<sup>1</sup>  $\mathbb{L}$  describes the class of ideal analog circuits that have an infinite maximum precision (Figure 1). Real analog circuits, which have a finite maximum precision, are classified by the number of data values encoded on individual wires in the circuit. A circuit is described by a subset of  $\mathbb{L}$  designated as  $\mathbb{L}_n$ , where n specifies a whole number of truth values.

<sup>\* 101</sup> Lindley Hall, Department of Computer Science, (812) 855-7081, jwmills@iuvax.cs.indiana.edu. This research was sponsored by the National Science Foundation, NSF MIP-10878, £ukasiewicz Logic Arrays.

<sup>&</sup>lt;sup>1</sup>  $L_1$  is replaced by L to avoid confusion when using  $L_n$  to denote subsets of  $L_1$ .

Figure 1. Relationship between Łukasiewicz logic and electronic circuits.

$\mathbb{L}_2$  is the most familiar subset of  $\mathbb{L}$ : it is the Boolean logic that describes binary digital circuits. Discrete multiple-valued circuits are described by subsets of  $\mathbb{L}$  with  $2 < n \le 16$ . Continuous-valued analog circuits are described by subsets of  $\mathbb{L}$  with  $2 \le n \le 2^p$ , where p is the maximum precision of the circuit in bits. Typically p falls in the range  $6 \le p \le 12$ .

Continuous-valued analog ŁLAs have a dual logical and algebraic semantics that makes them capable of both symbolic and numeric computation. Fuzzy controllers, neural networks, inference engines and general-purpose analog computers (GPACs) can be implemented with ŁLAs.

## 1.2 ŁUKASIEWICZ LOGIC ARRAYS

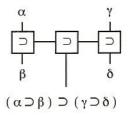

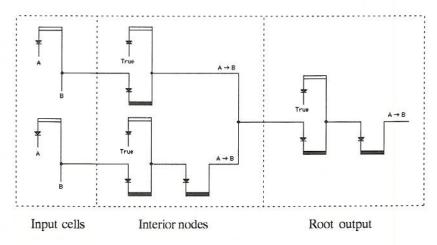

An £LA is organized as an H-tree array that implements a sentence schema of £. The processing elements of the £LA correspond to implications or negated implications in the sentence schema (Figure 2). £ukasiewicz implication is defined by the valuation function  $v(\alpha \supset \beta) = min(1, 1-\alpha+\beta)$ . Negated implication has a valuation function defined as  $v(\alpha \supset \beta) = max(0, \alpha-\beta)$ . Negated implication is identical to bounded difference ( $\bigcirc$ ) [3], but indicates its relation to implication:  $\supset \neg (\alpha \supset \beta)$ . The term implication is occasionally used to refer to both functions.

Figure 2. ŁLA H-tree corresponds to binary-tree-structured sentence schema.

Two implication circuits are described in this paper. The first is a one-diode negated implication circuit. The second is a three-transistor implication circuit with trim inputs that reduce error to less than 1% of full scale. Both circuits are derived from a 12-transistor Łukasiewicz implication circuit (ŁL9 implication). Two Łukasiewicz logic arrays (ŁLAs) are proposed that use area-efficient implementations of the one-diode and three-transistor implication circuits. The *diode tower* is

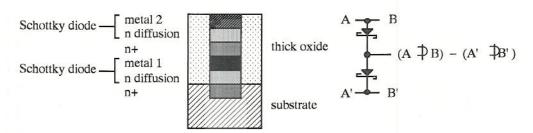

introduced to implement very dense ŁLAs. It is a three-dimensional VLSI structure composed of a vertically-stacked pair of Schottky-diode negated-implication circuits.

## 1.3 ADVANTAGES AND DISADVANTAGES OF VERY DENSE ŁLAS

Diode-tower and three-transistor  $\pm LAs$  contain more implications than previous  $\pm LAs$ . The diode-tower  $\pm LA$  is estimated to contain 36,000 implications in  $1800\mu \times 2000\mu$ , the area of a MOSIS Tiny Chip. Using the  $\pm L9$  implication cell the same area contains a maximum of 92 implications. The diode-tower  $\pm LA$  is as accurate as  $\pm L9$ , the prototype  $\pm LA$  that used the 12-transistor implication circuit.

The three-transistor £LA can be fabricated using nMOS current mirrors alone. The resulting array is less dense than the diode-tower £LA, but does not require the special process technology needed to fabricate diode towers. The three-transistor £LA contains a maximum of 1,990 implications in an  $1800\mu \times 2000\mu$  area, and is more accurate than £L9. The maximum error of the three-transistor £LA with trim inputs is 0.8% of full scale, while the maximum error for £L9 is 4% of full scale [4].

Both ŁLAs have the additional advantage that array inputs are the difference of two currents. This allows two input values for each input pin on the ŁLA integrated circuit package. However, even with twice the number of input values, ŁLAs are pin-limited devices. Application architectures must have numerous internal connections to fully utilize very dense ŁLAs.

#### 1.4 APPLICATION ARCHITECTURES REQUIRE VERY DENSE ŁLAS

Applications for Łukasiewicz logic arrays include fuzzy controllers, neural networks, tautology checkers for Ł, and general-purpose analog computers (GPACs) [5, 6, 7, 8, 9]. Arithmetic and logical functions are defined using implication or negated implication [3, 6]. A specific processor is constructed by mapping arithmetic and logical functions with varied precision to one or more ŁLAS [1, 3, 6, 7].

Architectures for these applications can not be implemented with the prototype ŁLAs, which contain too few implications. The Achernar ŁLA compiler typically outputs sentences containing hundreds of implications, with many internal and few external connections [10]. ŁL9, the prototype ŁLA, has only 32 implications per chip [4]. Practical architectures built with ŁLAs require at least 1,000 implications on a chip. ŁLAs of this density can be built with the area-efficient implication and negated implication circuits described in this paper.

## 2. AREA-EFFICIENT ANALOG CIRCUITS FOR ŁUKASIEWICZ IMPLICATION

#### 2.1 DERIVING THREE-TRANSISTOR AND ONE-DIODE IMPLICATION CIRCUITS

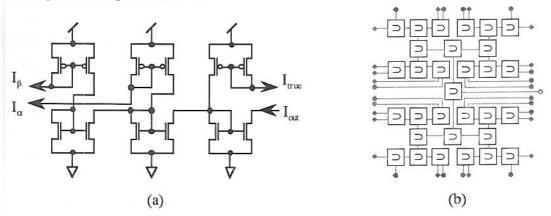

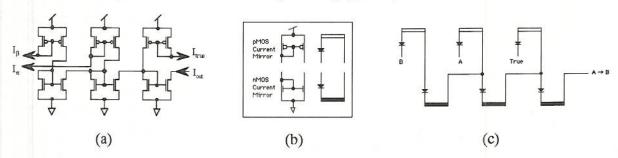

The £L9 Łukasiewicz implication cell is based on an earlier design that implemented negation and implication using Yamakawa's basic fuzzy logic cell [11]. The earlier design is simplified in £L9 to an implication cell with buffered input currents (Figure 3a). One £L9 array contains 32 implication cells (Figure 3b). Negation is programmed at the circuit's inputs by replacing the expression  $\neg \alpha$  with the equivalent expression  $\alpha \supset F$ .

Figure 3. 12-transistor implication cell (⊃) and ŁL9.

The 12-transistor implication cell of Figure 3a is unnecessarily complex compared to Yamakawa's six-transistor implication cell [3, 11] (Figure 4). However, a three-transistor implication cell and a one-diode negated implication cell (equivalent to Yamakawa's three-transistor bounded difference circuit) can be derived from the 12-transistor cell by removing redundant input buffers, and pairing implications in the array.

Figure 4. Six-transistor implication cell (⊃).

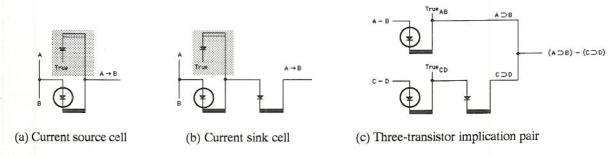

New schematic symbols are introduced to illustrate the derivation of the three-transistor and onediode implication cells. The symbols simplify the schematic of £L9 implication (Figure 5a). The pMOS and nMOS current mirrors are represented by U-shaped boxes, indicating their function as either current sources or current sinks (Figure 5b). An open bar at the top, like the bubble of a p-transistor, indicates a pMOS current mirror. A solid bar at the bottom indicates an nMOS current mirror. Diode-connected transistors are indicated by a diode. The resulting schematic for £L9 implication clearly shows its structure and operation (Figure 5c).

Figure 5. Original and simplified schematic of the ŁL9 stand-alone implication cell (2).

## 2.1.1 REMOVING UNNECESSARY CURRENT BUFFERS

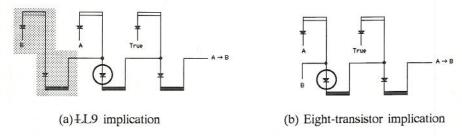

£L9 buffers the β input current before it is subtracted from the buffered α input current (Figure 6a, shaded). Buffering the β input in a binary tree array is redundant because no output drives more than one input. The current-mirror buffers for β also limit the value of β to the interval [0,1]. This is unnecessary because the diode-connected MOSFET (Figure 6, circled) keeps  $\alpha$ -β positive. The difference  $\alpha$ -β will fall within the interval [0,1] if the inputs  $\alpha$  and  $\beta$  lie in the interval [0,1]. Given this constraint, the β current-mirror buffers can be safely removed to yield an eight-transistor implication circuit (Figure 6b).

Figure 6. Removing redundant β current mirrors.

#### 2.1.2 SIMPLIFYING IMPLICATION IN AN ARRAY

The  $\alpha$  input of the eight-transistor implication circuit is mirrored only to invert the direction of the current flow, allowing implication cells to be connected into an array. However, pairing a current

source for  $\alpha$  with a current sink for  $\beta$  in the array removes the need for the  $\alpha$  input current mirror. The implication cells can then be simplified as a pair.

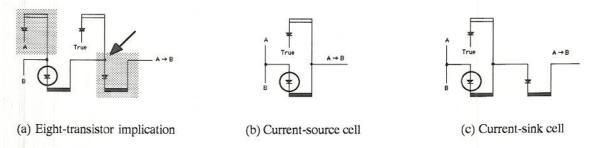

The current-source cell of the implication pair is derived by eliminating the  $\alpha$  input current mirror and the current mirror that provides a current sink at the output (Figure 7a, shaded). The output of the cell becomes a current source (Figure 7b). The current-sink cell of the implication pair is derived by eliminating the  $\alpha$  input current mirror alone. The output of the cell is a current sink (Figure 7c).

Figure 7. Deriving the current source and current sink cells.

In both cells the circled diode-connected MOSFET computes  $max(0, \alpha-\beta)$ . At the node pointed to by the arrow  $true - max(0, \alpha-\beta)$  is computed according to Kirchoff's Law. Because  $\alpha$  and  $\beta$  are constrained to lie in the interval [0,1] this is equivalent to  $min(true, true - \alpha + \beta)$ , the valuation function for implication.

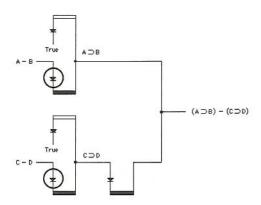

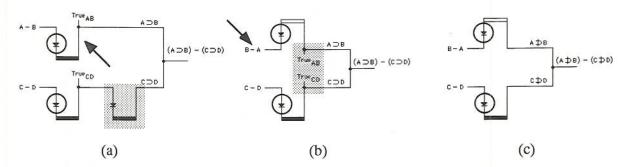

The current-source and current-sink cells are combined into an implication pair. Within the array, one child implication pair is connected to one input of the parent implication pair by a single wire. The wire carries a current whose value is  $\alpha$ - $\beta$ , where  $\alpha$  is the output of the child's current-source cell and  $\beta$  is the output of the child's current-sink cell (Figure 8).

Figure 8. Paired implication averages five transistors per implication circuit.

Figure 9. Internal components of ŁLA using paired implication.

ŁLAS built from implication pairs have three internal components: input cells, interior paired-implication cells, and a root cell whose output is a current-sink cell (Figure 9). Input cells at the leaves of the array are driven by current sinks. The  $\beta$  input is a current sink, but the  $\alpha$  input must be inverted with a current mirror to provide a current source. Interior nodes of the binary tree are composed of paired implication cells. The root output is a current-sink implication cell because its output is used directly. When cascading ŁLAS, the difference between the outputs of two lower-level ŁLAS is computed by the input cell of the next-higher ŁLA.

#### 2.1.3 THREE-TRANSISTOR IMPLICATION

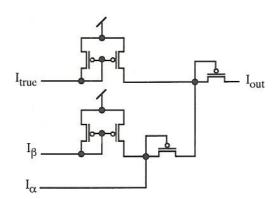

The five-transistor implication cell can be reduced to a three-transistor cell by removing the *true* reference current-mirror buffers (Figure 10, shaded). The reference currents are already generated by an array of current mirrors elsewhere on the 4LA. This current-mirror array must be implemented with pMOS current mirrors to provide current-source outputs instead of current sinks.

Figure 10. Removing true reference current mirrors.

The *true* reference currents can be used to adjust the output value of the paired implication cell. The reference current-mirror array is separated into one array of *true* references for the current-

source cells and another array for the current-sink cells. Each array is driven by a separate external input. Adjusting these inputs with respect to each other changes the location of the minimal error in each quadrant of the circuit's output. This adjustment can be used to compute functions with improved accuracy, although the precision of the circuit is unchanged.

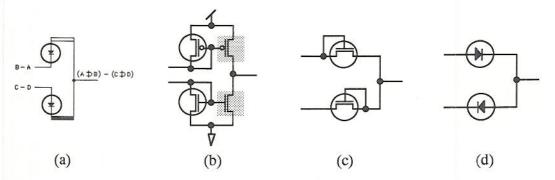

## 2.1.4 ONE-DIODE NEGATED IMPLICATION

The implication cell can be reduced to a single diode by transforming it to negated implication. In this process two-transistor and one-transistor negated implication cells are described. All active elements of the implication pair except the diode-connected MOSFET are removed, which is replaced by one diode.

The first step in the transformation is to remove the current sink in the current-sink cell (Figure 11a, shaded). Next, the sign of the *true* reference current is changed. To accomplish this the current-source cell is "inverted" by changing the nMOS current mirror to a pMOS current mirror, and the *true* reference current to a current sink (Figures 11a and 11b). The sign of the  $\alpha$  and  $\beta$  inputs must be reversed to preserve the computation of  $min(true, true - \alpha + \beta)$  (Figure 11b, arrow). The *true* reference currents are removed because their signs are opposite; they subtract out according to Kirchoff's Law (Figure 11b, shaded). A pair of two-transistor negated implication cells remain (Figure 12c). Each cell computes  $max(0, \alpha-\beta)$ .

Figure 11. Inverting current source cell polarity to eliminate reference currents.

The simplified schematic is expanded to show the derivation of the one-diode implication circuit (Figure 12a is equivalent to Figure 12b). The transistors that implement the current source and current sink outputs (Figure 12b, shaded) are not needed if the output voltage is sufficient to forward-bias the next diode-connected MOSFET in the array. (If not, the voltage can be restored by inserting a buffer.) Thus each current mirror can be replaced by a diode-connected MOSFET (Figure 12c). Substituting a p-n junction diode or a Schottky diode for the diode-connected MOSFET yields the one-diode implication cell (Figure 12d).

Figure 12. Reducing current mirrors to diodes.

Analog computers of the 1950's and 1960's used diodes to build special function generators [12, 13]. However, the link between these special function generators and Łukasiewicz logic was not recognized, although Wilkinson described an "analog diode logic" that is equivalent to Łukasiewicz logic [14]. Mead's innovations in analog VLSI for neural systems [15], the use of Łukasiewicz logic as a foundation for approximate reasoning systems, and the advent of practical ŁLAs point to the renewed growth of analog computing after a 30-year hiatus.

## 2.2 EVALUATING THE THREE-TRANSISTOR AND ONE-DIODE IMPLICATION CIRCUITS

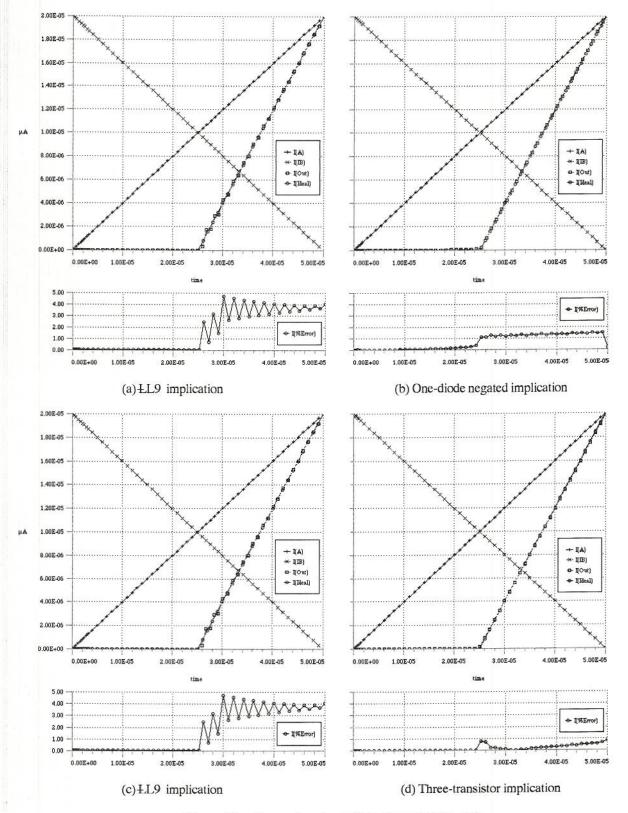

The results of simulating the ŁL9, the three-transistor, and the one-diode implication cells are shown. Level 3 of Spice is used because it most closely matches the measurements obtained from ŁL9. All simulations use the MOSIS process parameters for the ŁL9 fabrication run.

The "half-notch" function is simulated. It is defined by the expression  $\neg$  ( $\alpha \supset \neg \alpha$ ). The maximum error of the £L9 simulation is near 5% (Figure 13a and 13c), which is greater than the 4% error of an untrimmed £L9. The one-diode implication cell has a maximum error of 1.5% (Figure 13b). The three-transistor implication cell has a maximum error of 0.8% (Figure 13d). The smaller error in the one-diode implication cell is probably due to fewer active components, which reduce the noise in the cell's output. The three-transistor cell uses the *true* reference inputs to trim the cell's output. Varying the trim inputs is equivalent to varying the gain ratio between the current-source and current-sink implication cells in each pair, which reduces the error in the output.

Measurements of £19 show that its typical error is less than 2%, with a mean error less than 0.5% [1, 4]. This suggests that the results of simulating the three-transistor and the one-diode implication cells are plausible.

Figure 13. Comparing simulations of implication cells.

## 3. VERY DENSE ŁLAS

Two new ŁLAs are proposed in this paper. The first is a trimmable ŁLA based on the three-transistor implication cell. It is referred to as the three-transistor ŁLA and is similar to the prototype ŁLA. The second is a very dense ŁLA based on one-diode negated implication. The negated implication circuits are implemented in pairs, using two Schottky diodes stacked vertically. This three-dimensional VLSI structure is called a *diode tower*, so the ŁLA incorporating it is referred to as a diode-tower ŁLA.

#### 3.1 THREE-TRANSISTOR ŁLAS

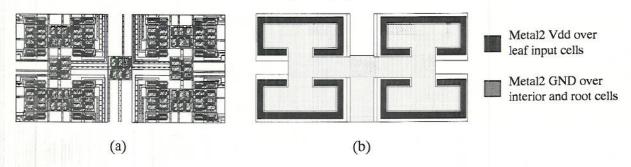

The three-transistor ±LA is smaller than ±L9 because it contains fewer transistors, and because those transistors are the same type. Because only nMOS transistors are used, no area is wasted to separate p-wells and n-wells internally. The pMOS current mirrors in the leaf input cells and the *true* reference current mirror array are placed around the edge of the ±LA. The nMOS current mirrors are grouped in the interior and root nodes (Figure 14a). The electrical isolation and heat dissipation of the ±LA is improved by covering the pMOS devices with a metal2 V<sub>dd</sub> plane; the nMOS devices are covered with a metal2 GND plane (Figure 14b).

Figure 14. Layout of 31-cell ±LP-3FET array.

#### 3.2 DIODE TOWER + LAS

A three-dimensional VLSI structure, the *diode tower*, is proposed to implement very dense ŁLAs. A diode tower is a vertically-oriented one-diode implication pair embedded in a silicon dioxide matrix. Diode towers can be constructed from p-n or Schottky diodes. P-n diode towers can be fabricated using three-dimensional silicon-on-insulator process technology, which has already been developed for MOSFETs. P-n diode towers are prevented from becoming avalanche diodes [16] by the central output connection of the diode tower. Diode towers can also be fabricated using bulk CMOS processes by intentionally building Schottky diodes, the normally unwanted devices that result when metal directly contacts diffusion.

Mills

In the proposed Schottky diode tower, the metal-diffusion contacts are not disabled by a layer of heavily-implanted n+ diffusion, except where an ohmic connection is desired between the diodes in the diode tower (Figure 15). The integral metal layers in the Schottky diodes are extended as global routing planes. N+ diffusion locally connects buried contacts in the substrate (Figure 16a).

Figure 15. Diode tower.

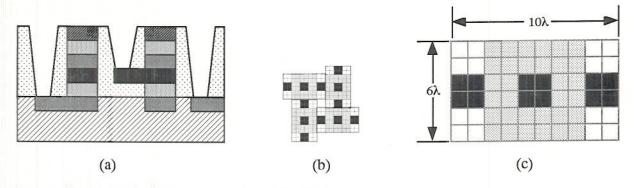

Using diode towers standard-cell ŁLAs can be designed as a *sea of implications*. These devices bring contacts for connections between cells to the surface of the ŁLA and leave them open for routing at a later time (Figure 16a). One diode-tower (two implication cells) can be constructed within a  $6\times10\lambda^2$  area (Figure 16c) and tiled as shown to give four diode towers (eight implications) per  $14\lambda^2$  (Figure 16b). In this configuration a  $2\mu$  process would fit a maximum of 36,000 implications into a MOSIS Tiny Chip, and approximately  $1.3\times10^6$  implications into a one cm<sup>2</sup> die. This is the equivalent of  $10^4$  fuzzy rules or algebraic functions.

Figure 16. Diode tower array.

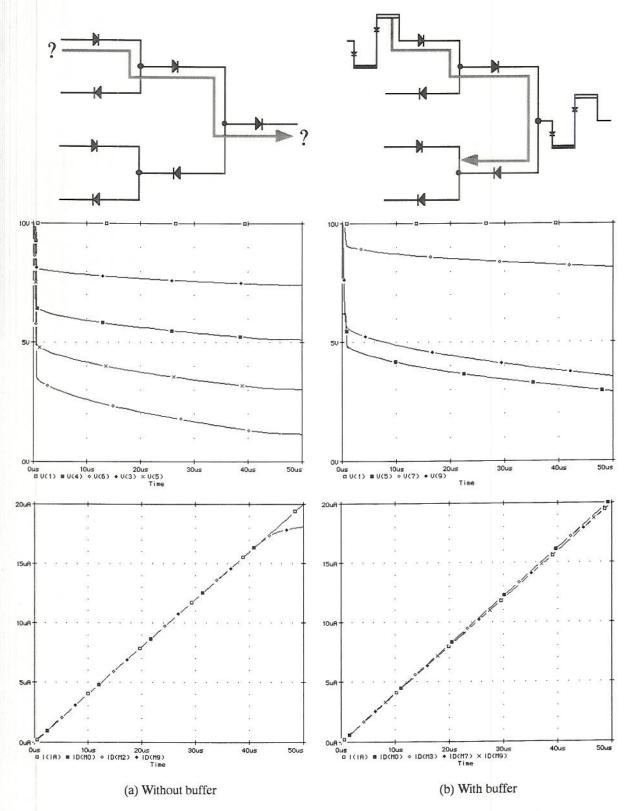

The one-diode negated implication circuit has the disadvantage that the voltage drop across successive diodes in a chain will be insufficient to forward-bias the last diode in the chain (Figure 17a). Current-mirror buffers, similar to buffers in digital logic, must be inserted to prevent this from occurring (Figure 17b). A buffer is needed after every three diode-connected MOSFETs, which have a voltage drop of 1.2 volts, or every 10 to 15 Schottky diodes, which have a voltage drop of 0.25 volts.

Figure 17. Unbuffered and buffered one-diode negated implication chains in an ŁLA.

## 3.3 ADVANTAGES AND DISADVANTAGES OF VERY DENSE ŁLAS

Diode-tower and three-transistor  $\pm LAs$  are denser than previous designs. In an  $1800\mu \times 2000\mu$  area the diode-tower  $\pm LA$  contains 36,000 implications, while the three-transistor  $\pm LA$  contains 1,990 implications. Only 92 12-transistor implications fit into the same area. Table 1 summarizes the improvements.

| ŁLA                    | Cell layout (all to same scale) Cell type, number of components | Function | Area of 31 cell array <sup>2</sup> | Maximum implications |                        |

|------------------------|-----------------------------------------------------------------|----------|------------------------------------|----------------------|------------------------|

|                        |                                                                 |          |                                    | "Tiny" chip          | 1 cm <sup>2</sup> area |

| £1.9                   | stand-alone MOSFET, 6 pTrans + 6 nTrans                         | α⊃β      | 888μ x 1366μ                       | 92                   | 2,550                  |

| ∔LA-3FET               | Cascoded MOSFET, 3 nTrans                                       | α⊃β      | 170μ x 329μ                        | 1,990                | 55,400                 |

| +LA-D-3d<br>(proposed) | Cascoded diode tower, 1 Schottky diode                          | α⊅β      | 48μ x 48μ                          | 36,000               | 1,300,000              |

Table 1. Optimization of ŁLAs.

A disadvantage of diode-tower LLAs is that the voltage drop across successive diodes in a chain will be insufficient to forward-bias the last diode in the chain. Circuits similar to buffers in digital logic must be inserted to prevent this from occurring.

An advantage of three-transistor £LAs is that they can be fabricated using nMOS current mirrors alone. The resulting array is less dense than the diode tower array, but functions more accurately. The trim inputs can be adjusted to reduce error to less than 1% of full scale. This £LA is more accurate than the prototype £L9 because its output can be trimmed using independent positive and negative reference currents.

Both ŁLAs have the advantage that the number of inputs is twice the number of input pins on the package. This is because each input is the difference of two currents, which can be computed externally and carried on a single wire.

Values measured from MAGIC layouts for MOSIS 2μ SCPE Orbit process, or estimated for 2μ 3-D process.

## 4. SUMMARY AND CURRENT WORK

A one-diode circuit for negated implication (\$\Pi\$) and an adjustable three-transistor implication circuit with maximum error less than 1% of full scale were described. Two £LAs were proposed that use area-efficient implementations of the one-diode and three-transistor implication circuits. The very dense diode-tower £LA contains 36,000 implications in an area that previously held 92 implications; the three-transistor £LA contains 1,990 implications. Both £LAs double the number of inputs per pin on the IC package.

Diode tower designs for very-dense three-dimensional ŁLAs are now being simulated. If these designs are successful, then the next generation of ŁLAs may fit as many as 1.3 million implications into a one cm<sup>2</sup> area. Very dense ŁLAs are needed to make ŁLA-based architectures for neural networks and fuzzy controllers practical.

$\pm$ LA simulators are being applied to neural networks and fuzzy controllers. The Sharks & Jets constraint propagation network has been simulated with  $\pm$ LAs [17]. A simple fuzzy controller for an air conditioner has been designed that uses three implications to implement a continuously-varying number of rules. This fuzzy controller fits into a  $100\mu^2$  area.

Achernar, believed to be the first analog compiler since the 1970's, is being developed by Andy Heininger, a graduate student in the Analog VLSI Laboratory. Achernar compiles algebraic expressions to Łukasiewicz implication, uses tree-pattern matching to minimize the tree, and applies peephole optimizations to further simplify the expression. The output of Achernar is a sentence schema for an ŁLA from which a MAGIC layout of a very dense ŁLA can be extracted.

#### ACKNOWLEDGEMENTS

Professor Steven D. Johnson made numerous useful comments which improved the presentation of this research.

Charles A. Daffinger designed £L9, the prototype £LA, and was co-author on the first papers describing £LAs. He was 26 years old when he died in a spelunking accident in January, 1991, immediately before he could begin his doctoral research into high-precision £LAs. Charles was an energetic, motivated student. During 1990 he completed a minor in electrical engineering, a subject not offered at Indiana University, by commuting 250 miles weekly to Purdue University. Charles attended the 20th ISMVL in Charlotte, North Carolina, where the first paper describing £LAs was presented.

#### REFERENCES

- [1] Mills, J. W., M. G. Beavers, and C. A. Daffinger. 1990. Lukasiewicz Logic Arrays. *Proceedings of 20th International Symposium on Multiple-Valued Logic*.

- [2] Lukasiewicz, J., and A. Tarski. 1930. Untersuchungen über den Aussagenkalkül. Comptes rendus des séances de la Société des sciences et des lettres des Varsovie Classe III (23): pp. 30-50.

- [3] Yamakawa, T., T. Miki, and F. Ueno. 1985. The design and fabrication of the current mode fuzzy semicustom IC in the standard CMOS IC technology. Proceedings of IEEE 17th International Symposium on Multiple-Valued Logic. IEEE Computer Society Press. pp. 76-82.

- [4] Mills, J., and C. Daffinger. 1990. CMOS VLSI Lukasiewicz Logic Arrays. Proceedings of Application Specific Array Processors. Princeton, New Jersey:

- [5] Alspector, J., R. B. Allen, V. Hu, and S. Satyanarayana. 1987. Stochastic learning networks and their electronic implementation. *Proceedings of Neural Information Processing Systems—Natural and Synthetic*. Denver, Colorado, November 8-12.

- [6] Beavers, M. G. 1991. "Topics in Lukasiewicz Logics." Ph.D., Indiana University, Bloomington, Indiana.

- [7] Mills, J., and C. Daffinger. 1990. An Analog VLSI Array Processor for Classical and Connectionist AI. Proceedings of Application Specific Array Processors. Princeton, New Jersey:

- [8] Rubel, L. A. 1985. The Brain As an Analog Computer. J. Theoretical Neurobiology 4 (July 23):

- [9] Rubel, L. A. 1989. Digital Simulation of Analog Computation and Church's Thesis. *Journal of Symbolic Logic* 54 (3): pp. 1011-1017.

- [10] Mills, J. W., and A. Heininger. Achernar: A compiler for Lukasiewicz logic arrays. (in preparation).

- [11] Yamakawa, T., and T. Miki. 1986. The current mode fuzzy logic integrated circuits fabricated by the standard CMOS process. *IEEE Transactions on on Computers* C-35 (2): pp. 161-167.

- [12] Hausner, A. 1971. Analog and Analog/Hybrid Computer Programming. Englewood Cliffs, New Jersey: Prentice-Hall.

- [13] Korn, G. A., and T. M. Korn. 1964. Electronic Analog and Hybrid Computers. New York, New York: McGraw-Hill.

- [14] Wilkinson, R. H. 1963. A Method of Generating Functions of Several Variables Using Analog Diode Logic. *IEEE Transactions on Electronic Computers* EC-12 (2): pp. 112-128.

- [15] Mead, C. 1989. Analog VLSI and Neural Systems. Edited by L. Conway, C. Seitz and C. Koch. VLSI System Series/Computation and Neural System Series. Reading, Massachusetts: Addison-Wesley.

- [16] Abraham, G. 1984. Mulitple-valued negative resistance circuits. In Computer Science and Multiple-Valued Logic. Edited by D. C. Rine. New York: Elsevier Science Publications.

- [17] Rumelhart, D. E., and J. L. McClelland. 1986. Parallel Distributed Processing. Cambridge, Massachussetts: MIT Press.