djengt

## TECHNICAL REPORT NO. 331

## DDD – A Transformation System for Digital Design Derivation

by

Bhaskar Bose

May 1991

COMPUTER SCIENCE DEPARTMENT

INDIANA UNIVERSITY

Bloomington, Indiana 47405-4101

# DDD - A Transformation System for Digital Design Derivation\* Reference Manual

by

Bhaskar Bose Computer Science Department Indiana University Bloomington, Indiana

DDD - A Transformation System for Digital Design Derivation Reference Manual

by

Bhaskar Bose

May, 1991

<sup>\*</sup>Research reported herein was supported, in part, by the National Science Foundation under grants numbered DCR85-21497, MIP87-07067 and MIP89-21842.

Dear Reader,

The DDD system is constantly undergoing changes as researchers continue to study hardware design in the context of an algebraic framework. This manual is intended to document the current status of the system and acknowledges the dynamics of the system it attempts to characterize. It is the sincere hope of the author that this document provides the reader with an understanding of the system and continues to be updated as the system evolves.

Bhaskar Bose

## **Table of Contents**

| 1 Introduction                                                                                                                                               |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2 Derivation Path                                                                                                                                            | 5               |

| 3 Specification  3.1 Scheme Syntax  3.2 Hardware Specifications  3.2.1 Expressing Control  3.2.2 Expressing Architecture  3.3 An Example: Single Pulser  1.5 | 7 8 9           |

| 4 Control Abstraction and Architecture                                                                                                                       | 5               |

| 5.4 Partial Evaluation of Selectors                                                                                                                          | 1 2 3 4 6 6 6 8 |

| 6 Register Transfer Table                                                                                                                                    | 11<br>12        |

| 7 Projection                                                                                                                                                 | 19              |

| 8 Input/Output                                                                                                                                               | 55              |

| O Doigy Interface                                                                                                                                            | 5               |

| 10 I Roolean Equation Communication Communic | 6   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10.1 Boolean Equation Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0   |

| 10.1.1 Generating Boolean Equations from Selectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0   |

| 10.1.2 Concreting Decleral Equations from Selectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61  |

| 10.1.2 Generating Boolean Equations from Stream Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62  |

| 10.2 ESPRESSO Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63  |

| 10.3 EQN Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65  |

| 10.4 PLA Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66  |

| 10.5 Altera Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| terorences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79  |

| ppendix A. DDD Quiel- D. C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Appendix A: DDD Quick Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A-1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| appendix B: Type Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B-1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Example 1: A Single Pulser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C-1 |

| Example 1: A Single Pulser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.1 |

| Example 2: A Black Jack Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C-1 |

| Zimmple 2. A Diack Jack Widelinie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C-7 |

## DDD - A Transformation System for Digital Design Derivation\* Reference Manual

Bhaskar Bose Computer Science Department Bloomington, Indiana

## 1 Introduction

DDD (<u>Digital Design Derivation System</u>) is a transformation system that implements a design algebra for synthesizing digital circuit descriptions from high level functional specifications. The system reflects a formal approach to digital design synthesis based on the algebraic manipulation of purely functional forms.

The system is intended to provide a well founded, mechanized, algebraic tool set for design synthesis. DDD is implemented in the Lisp dialect Scheme [11] as a collection of transformations that operate on s-expressions. Transformations are applied manually by the designer, either interactively or by creating a script, at various stages of the design process in order to derive hardware implementations. The hardware descriptions that are manipulated by DDD are written in Scheme and may be executed (with syntax extension) as Scheme programs.

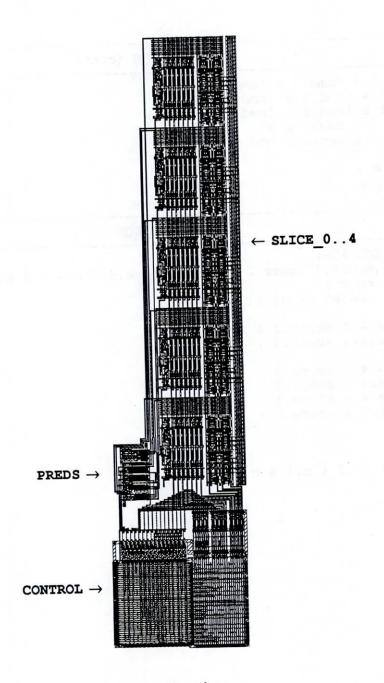

DDD derives a technology independent set of digital circuit descriptions which are projected to binary representations. Boolean equations are then generated from these descriptions and are integrated with existing logic synthesis tools, such as boolean equation minimizers, PLD assemblers, and VLSI layout generators.

## 1.1 Design by Algebraic Transformation

In "Synthesis of Digital Designs from Recursion Equations" [9], Johnson defines a formal approach to hardware synthesis based on the algebraic manipulation of purely functional forms. In this framework, the discipline of applicative program design style is adapted to hardware synthesis.

Design is viewed as a translation of notation, starting with an abstract specification ranging over abstract data types and deriving an intended target description called an *implementation* and a physical object called a *realization*. This process may be viewed as a translation between dialects of recursive expressions, and can be expressed in the following diagram:

<sup>\*</sup>Research reported herein was supported, in part, by the National Science Foundation under grants numbered DCR85-21497, MIP87-07067, and MIP89-21842.

$$D_0 \xrightarrow{\tau_0} D_1 \xrightarrow{\tau_1} \dots \xrightarrow{\tau_{k-1}} D_k$$

$D_0$  represents a source description and  $D_k$  an implementation. The arcs may be enumerated from  $\tau_0$  to  $\tau_{k\cdot l}$  and represent applications of transformations. Thus design is defined as an initial specification  $D_0$ , and a derivation - the sequence of transformations  $<\tau_0,...,\tau_{k\cdot l}>$ .

The first step in design is to write a functional specification. The design proceeds by applying a series of transformations on an evolving description. The final form is a circuit description ranging over binary values that are integrated with logic synthesis tools to generate hardware.

The method provides a secure path to hardware. In the formal discussion [9], each transformation is correctness preserving. The implementation is said to be correct by construction. The notion of "correctness" is defined as: Given a specification S, and a transformation  $\tau$ ,  $\tau(S)$  results in an expression that will compute the same function as the initial specification.

The specifications are written in a functional programming language and are directly executable. Each derived form is also executable (with syntax extension). The source for synthesis is also the same object for *simulation*. For instance, the execution trace of the specification may also be used for *test vector generation*. An example of this may be found in [2]. A common source description, from which varying information is derived, reduces the chance of inconsistencies between the specification/implementation, and simulation model.

The notion of abstraction is fundamental. Control abstraction, data abstraction, and hierarchical abstraction define the design process. Control abstraction forms the basis of separating control and architecture from the initial specification. Data abstraction allows for the manipulation of architectural components. And finally, hierarchical abstraction allows for the translation to lower levels of description to the point of a realization.

The incorporation of *representations* may be introduced at any stage in the derivation. This allows the opportunity to postpone representation decisions to a later point in the design.

Verification is an interdependent facet of this methodology. Although mechanical derivation implements algebra that assures correct hardware - too many facets of design are unaccounted for in any given transformation system. In principle, the incorporation of a verification system will allow the engineer to call upon insight and experience to produce an efficient design, which is then simply certified by a computer. This is developed further in [3].

## 1.2 About this manual

Section 2 characterizes the derivation path in a design. Each of the sections (Section 3 to Section 10) discuss a facet of the derivation path. Each section has a heading which highlights which stage of derivation path is being addressed. Each section is divided into two parts.

First, an informal discussion on relevant strategic issues, and transformational algebra are presented. The second part, defines transformations that are implemented in DDD. Each transformation definition contains the name of the transformation and what its arguments are. A short description of the transformation, followed by an example application. Section 3 defines the input specification. Section 4 discusses the initial transformations which derive a structural description from a behavioral specification. Section 5 discusses algebra on structural descriptions. Section 6 discusses register transfer tables, a intuitive abstraction of structural descriptions. Section 7 discusses the projection of a description defined over an abstract basis to that of a description defined over some target basis. Section 8 discusses input/output extensions to Scheme. Section 9 discusses transducing scheme circuit descriptions into Daisy descriptions. Section 10 discusses the integration of DDD with logic synthesis tools.

Appendix A is a quick reference to all current DDD functions. Appendix B lists the forms of the objects that are manipulated by DDD. Appendix C contains two complete design examples. First, a simple single pulser circuit, SinglePulser, followed by a machine which implements the actions of a Black Jack dealer, BlackJack. Other examples not found in this text include a Stop-and-Copy garbage collector in VLSI [2], and an SECD machine [15].

In DDD, a sequence of transformations are applied to an initial specification defining a *derivation path* to an implementation. The path is expressed in the following diagram:

$$I \to C_I {}^{\bullet}S_I \dots \to C_n {}^{\bullet}S_n /\!\!/ F \xrightarrow{\rho_{\beta}} C_{\beta} {}^{\bullet}S_{\beta} /\!\!/ F$$

I represents an initial specification. It is iterative - the class of recursion schemata that characterizes sequential control. The initial specification is expressed in terms of a complex basis consisting of abstract operations and predicates, in addition to concrete operations and objects. Some examples are arrays of integers, memories, stacks, and arithmetic. The complex/concrete distinction is subjective and hierarchical. Thus I is defined at some intended level of description.

Initial transformations separate control and architecture, and derive a sequential system description:  $C_1 \circ S_1$ . C denotes a descision combinator representing control, and S denotes a structural component representing architecture. The  $\bullet$  operator denotes the composition of C and S.  $C_1 \circ S_1$  has the same complex basis as I, but the interpretation is based on the model of streams. Whereas before, variables ranged over values, they now denote sequences of values.

The algebra supported by DDD allows for the logical and physical decomposition of design. These design tactics alter the derivation path and sketch a complex design space with many possible paths between specification and implementation. The dotted notation ... in the ideogram denotes this one-to-many correspondence.

$C_n \cdot S_n || F$  is system description at some level of refinement. Complex data types present in  $S_I$  have been factored as a system of abstract components denoted by F. The || suggests a communicating system. As complex signals are factored, DDD generates signals to maintain the correct connectivity. Factorization is a central part of DDD's transformations.

$C_{\beta} \cdot S_{\beta} /\!\!/ F$  is the projection of  $C_{n} \cdot S_{n} /\!\!/ F$  to a target representation,  $\beta$ . Representations are input to the system in the form of a projection function denoted by  $\rho_{\beta}$ .

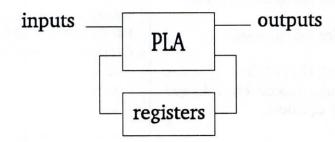

Completing the path to hardware, abstract descriptions are projected to binary representations. Boolean equations are then generated. The equations can be implemented with MSI components directly, or can serve as inputs to a programmable logic device (PLD) programmer, or can be used as input to VLSI tools to generate PLAs, gate matrix, or standard cell layouts.

Specifications are written in Scheme. The specifications are written in a purely functional style where there are no side-effects. Descriptions are built from applicative terms, constants, identifiers, conditional expressions, case statements, and function definitions, and express synchronous systems. The specification is a control algorithm, as well as a description of architecture. Both control and architecture are derived from such specifications. DDD manipulates a concrete syntax of functional s-expressions in Scheme.

## 3.1 Scheme Syntax

Scheme is a statically scoped, applicative order, dialect of Lisp, which is well suited for symbolic manipulation. The language definition is a small core of syntactic forms from which all other forms are built. These core forms, a set of extended syntactic forms derived from them, and a library of primitive procedures make up the full Scheme language. An informal introduction to some of the basic forms are described in this section. A complete language definition can be found in [11].

Scheme supports operations on structured data such as *strings*, denoted with double quotes, "abcd", lists, denoted by parenthesized sequences,  $(l_1 \ l_2 \ ... \ l_n)$ , and vectors. Scheme also supports operations on more traditional data such as numbers and symbols. Programs are made up of forms (lists), identifiers (symbols), and constant data (strings, numbers, vectors, quoted lists, quoted symbols, etc.). A brief description of the forms used in DDD are described below.

Procedures are defined with function expressions. A function expression has the form

The identifiers (id ...) are the formal parameters of the procedure, and the sequence of expressions expl exp2 ... is its body.

Objects can be associated with a name at top level with a top-level definition. A top-level definition has the form

(define id exp)

The identifier id is bound at top-level, to the value of the expression exp.

Two forms of conditional expressions are used in DDD, an if-then-else expression, which has the form

(if test consequent alternative)

which returns the consequent if the test is true, and the alternative otherwise; and a case-

expression of the form

which returns the value of the last exp of the corresponding label key equals val.

Local definitions are made with let and letrec expressions. A let expression has the form

Creates a local binding in which each identifier *id* is bound to the value of the corresponding expression *val*. These bindings are valid in the body of the let *expl exp2* ...

A syntactic form similar to let, but allows mutually recursive bindings is letrec. A letrec expression has the form

## 3.2 Hardware Specifications

A general form of the specification is given below. A circuit is defined by a set of mutually recursive function definitions,  $S_0,...,S_Q$ , referred to as *state definitions*. Each state definition is a conditional expression representing a point of control. ( $i_1 i_2 ...$ ) denotes a set of inputs to the circuit, and ( $S_{init} r_{linit} r_{linit} ... r_{Ninit}$ ) denotes the initial control point and state for the machine.

Each state definition has a uniform parameter list,  $(\mathbf{r_1} \ \mathbf{r_2} \ \dots \ \mathbf{r_N})$  denoting a set of registers, defining the state of the machine, and i/o ports. However, since the level of abstraction is arbitrary, the notion of registers are abstract. The list of registers may contain arbitrary objects such as registers, memories, stacks, and communication channels. The set of registers is an initial estimation of architecture and represents architectural components with state.

```

\begin{array}{c} (\text{define CIRCUIT} \\ (\text{lambda } (i_1 \ i_2 \ ...) \\ (\text{letrec} \\ \\ ((S_0 \ (\text{lambda } (r_1 \ r_2 \ ... \ r_N) \ \text{exp}_0)) \\ (S_1 \ (\text{lambda } (r_1 \ r_2 \ ... \ r_N) \ \text{exp}_1)) \\ \\ ... \\ (S_Q \ (\text{lambda } (r_1 \ r_2 \ ... \ r_N) \ \text{exp}_Q))) \\ (S_{\text{init}} \ r_{\text{linit}} \ r_{\text{2init}} \ ... \ r_{\text{Ninit}})))) \end{array}

```

where exp can be: a let expression

an if statement

(if pred exp<sub>1</sub> exp<sub>2</sub>)

a case statement

(case pred (id<sub>1</sub> exp<sub>1</sub>) (id<sub>2</sub> exp<sub>2</sub>) ...)

or a control point invocation

(S val<sub>1</sub> ... val<sub>N</sub>)

where val denotes an expression defined in the ground type at some intended level of abstraction. Valid terms for val are ?, signals, constants, integers, booleans, arithmetic operations, boolean operations, routing primitives, and operations on abstract data types. ? is a special character which denotes a "don't care" term.

The *let expression* provides a means of defining combinational signals, and associating a name with that expression.

The *if* and *case statement*, implement a conditional control construct dependent on a decision point **pred**. In the case of an *if statement*, **pred** can be any boolean expression defined in the ground type. In the case of a *case statement*, **pred** can be any expression defined in the ground type. These conditionals are implemented in control, while conditionals expressed within a *control point invocation* are implemented in the data path.

A control point invocation, (S  $val_1 ... val_N$ ), is a function invocation which denotes a parallel assignment to a set of registers and a transfer of control to state S. Operations expressed here are implemented in the data path.

Operations on abstract data types are expressed as

(op object x y ...)

where op is an operation defined on the abstract data type object, and x and y, are arguments. For example, operations on a memory object, MEM, may be written with the expressions (MemWrite MEM Addr Data), and (MemRead MEM Addr). A stack object, STACK, may be written with the expressions (Push STACK Data), (Pop STACK), (Top STACK), and (Empty? STACK).

## 3.2.1 Expressing Control

The specification is *iterative* - each state definition, S, is a conditional expression in which the alternatives are tail-recursive, and is equivalent to the class of schemata associated with finite state machines. The correspondence between the iterative specification and finite state ma-

chines is illustrated in the mappings on the following page from partial state definitions to Algorithmic State Machine (ASM) [16] fragments. The ASM notation is derived from software flowchart notation, and provides a means of expressing abstract algorithms while supporting the conversion of the algorithm into hardware. Control flows through a sequence of states, denoted by a rectangle, based on the position in the control algorithm, and the values of the relevant status variables. Given a present state, the next state is determined unambiguously. To express operations on the architecture, operations are placed within the appropriate state rectangle. Conditional branches are denoted with a diamond. Operations on the architecture which occur conditionally are placed in ovals on the appropriate conditional branch. The following constructs show how a simple sequence of state transitions, a conditional branch, and a multi-way branch are expressed in the language. (note: Architectural details have been suppressed for the sake of clarity and are addressed subsequently.)

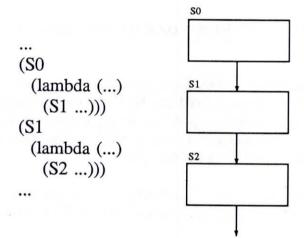

A sequence of state transitions:

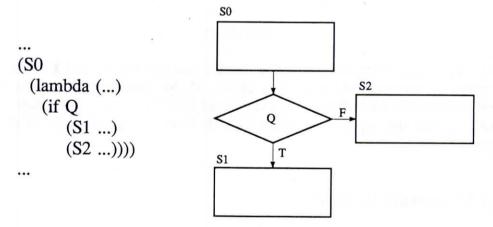

A conditional branch:

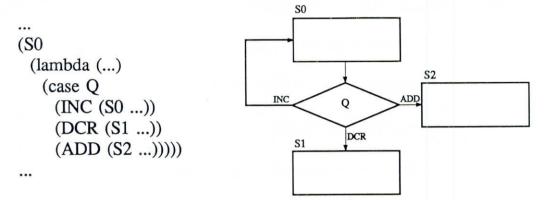

A multi-way branch:

## 3.2.2 Expressing Architecture

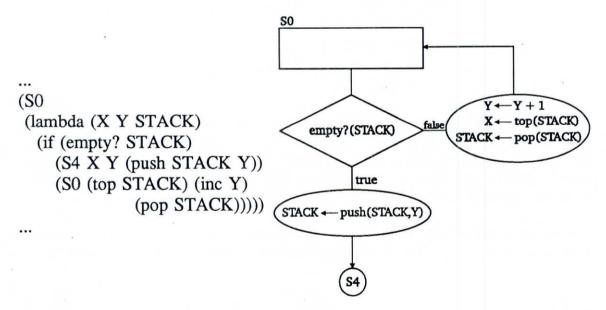

Architecture is expressed in the *formal parameters*, the *let expression id/val pairs*, and *vals* in the *control point invocations*. Consider the following state definition and ASM fragment which illustrates how the formal parameters and vals in the control point invocations are used to define the architectural components and operations:

The formal parameters (X Y STACK) specify two registers X and Y, and a stack STACK. When STACK is empty, control is passed to state S4; the contents of X and Y remain unchanged; and the value of Y is pushed onto the stack. If STACK is not empty, control is passed to state S0; X is updated with the value of the top of stack; the contents of Y is incremented; and the stack is popped.

In order to execute the specification the operations empty?, push, pop, top, and inc, are defined in the ground type or basis at some level of abstraction. Suppose X and Y are defined

over integers, and STACK is represented by a simple list. Then the above operations may be defined by the following function definitions:

The level of abstraction at which the ground type is defined is purely a matter of choice. The ground type may just have easily been described in terms of a binary representation, or a combination of different levels of abstractions - X may range over binary numbers, while Y may be defined over integers. In the course of a design, various levels of abstraction of the basis may be supplanted while the specification remains unaltered.

Combinational terms may also be associated with a signal name using the let expression. In the next example, the (top STACK) operation from the previous example is associated with the signal Z.

```

(S0 (lambda (X Y STACK)

(let ((Z (top STACK)))

(if (empty? STACK)

(S4 X Y (push STACK) Y)

(S0 Z (inc Y) (pop STACK)))))

```

However, signals defined in let expressions are under specified. What is the value of **Z** outside the scope of the let expression in which it is defined? The DDD system defaults the value of **Z** to **nop** which denotes a "do nothing" operation.

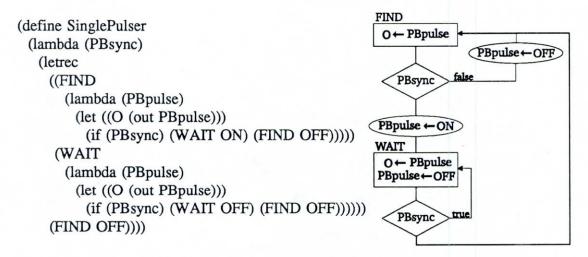

## 3.3 An Example: Single Pulser

Consider the specification of the *single pulser* circuit as described in [16], and its corresponding ASM. The example, though simple, illustrates a complete specification. For further examples see [6,15,5,Appendix C]. In the next few sections, this example is taken through the derivation system.

The SinglePulser senses the depression of the button, **PBsync**, and asserts an output signal, **PBpulse**, for a single clock pulse. Additional assertions of the output are not allowed until after the operator releases the button.

The circuit is defined as a two-state machine: FIND, and WAIT, that takes a synchronized input assertion from a push button: PBsync. The output of the system is O which carries the signal PBpulse, a synchronized output assertion. The initial invocation of the single pulser algorithm, cycles in the FIND state, until a true signal is asserted on PBsync. Control is then transferred to the WAIT state, with the value ON being asserted on the PBpulse signal. The algorithm cycles in the WAIT state, until a false is asserted on the PBsync signal. Control is then transferred back to FIND.

Initial transformations decompose the iterative specification into a control abstraction, called Select, and an architectural component, referred to as a structural specification defined as a set of mutually recursive stream equations. The control abstraction and structural specification are collectively referred to as a sequential system. The sequential system has the same abstract basis as the initial specification, but the interpretation is based on streams. Whereas before, variables ranged over instantaneous values, they now denote sequences of values over time.

### 4.1 The Stream Model

Sequential systems are modeled by streams. The symbol! denotes an element that has state. In this discussion it is referred to as a register.

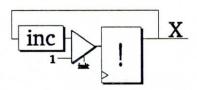

Consider a counter modeled as a stream.

$$X = 1 ! inc(X)$$

X denotes a stream of values 1,2,3,4,5,..., defined over integers.

X is a signal with state, and represents the output of the equation. The equation is initialized with the value 1. inc(X) denotes a combinational incrementor, whose input is X, and whose output is X+1. The stream equation may be characterized by the following circuit:

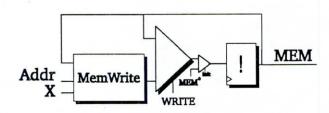

Another example is a memory modeled as a stream.

MEM = MEM<sup>0</sup>! (if WRITE (MemWrite MEM Addr X) MEM)

MEM denotes a stream of memories MEM<sup>0</sup>,MEM<sup>1</sup>,MEM<sup>2</sup>,MEM<sup>3</sup>,...

MEM<sup>0</sup> is the initial memory. If the WRITE signal is asserted, MemWrite will return a new memory object, with address, Addr, updated with value X. Otherwise, the memory is returned unchanged. It is important to note that the level of abstraction is arbitrary. In the first example values ranged over integers. In the second example values ranged over memories.

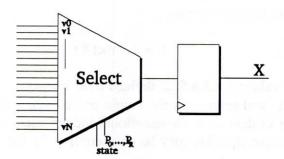

The characteristic stream equations derived by DDD have the form:

$$(X \leftarrow (\text{Select state } P_0 \dots P_R \ V_0 \ V_1 \dots V_N))$$

(a)

$(Y = (\text{Select state } P_0 \dots P_R \ V_0 \ V_1 \dots V_N))$  (b)

The ! symbol together with an initial value are denoted with the  $\Leftarrow$  symbol. Equations defined with  $\Leftarrow$  have state. Equations with a simple = are combinational. Select is a combinational decision combinator which returns one of the possible values,  $V_{\theta}$ ,..., $V_{N}$  as a function of state, and a set of status predicates,  $P_{\theta}$ ,..., $P_{R}$ . Select may be viewed as an N-input multiplexor, defined over abstract values, with control signals state, and  $P_{\theta}$ ,..., $P_{R}$ . The associated schematic for (a) is shown below. The schematic for (b) is similar to (a) with the omission of the register.

## 4.2 Deriving a Sequential System

The derivation of a sequential system from the initial specification are outlined in this section. For a formal discussion refer to [9]. The **SinglePulser** specification on page 13 from the previous section is used to illustrate the initial set of transformations.

```

(define SinglePulser

(lambda (PBsync)

(letrec

((FIND

(lambda (PBpulse)

(let ((O (out PBpulse)))

(if (PBsync) (WAIT ON) (FIND OFF)))))

(WAIT

(lambda (PBpulse)

(let ((O (out PBpulse)))

(if (PBsync) (WAIT OFF) (FIND OFF))))))

(FIND OFF))))

```

The first step introduces a control token, state, to represent each of the state definitions WAIT and FIND. A single loop form of the initial specification is constructed by adding state to the formal parameter list, changing each function invocation to a recursive call to SinglePulser, and constructing a case statement encoding which function is in control.

A decision combinator, or control abstraction is then derived by factoring all predicates and function invocations from the single loop form. The result is a control specification, Select, and an architectural description, SinglePulser, defined as a set of stream equations.

```

(define Select

(lambda (s p v0 v1 v2)

ON

(case s

PBpulse

OFF

Select

(FIND (if p v0 v1))

(WAIT (if p v2 v1)))))

((state \Leftarrow

(Select state (PBsync) WAIT FIND WAIT))

WAIT

(PBpulse ←

state

(Select state (PBsync) ON OFF OFF))

FIND

Select

(O =

(Select state (PBsync) (out PBpulse) (out PBpulse)

(out PBpulse))))

PBsync

```

(ItrSys->SingleLoop ItrSys) → SingleLoop

Takes an iterative system specification and returns the single loop form.

```

DDD> (define sp

' (define singlepulser

(lambda (pbsync)

(letrec

([find

(lambda (pbpulse)

(let ([o (out pbpulse)])

(if (pbsync) (wait on) (find off))))]

[wait

(lambda (pbpulse)

(let ([o (out pbpulse)])

(if (pbsync) (wait off) (find off))))])

(find off))))

DDD> (ItrSys->SingleLoop sp)

(define singlepulser

(lambda (state pbpulse)

(case state

[find

(let ([o (out pbpulse)])

(if (pbsync)

(singlepulser wait on)

(singlepulser find off)))]

[wait

(let ([o (out pbpulse)])

(if (pbsync)

(singlepulser wait off)

(singlepulser find off))))))

```

(SingleLoop->Select SingleLoop) → Select

Takes a single loop specification and returns the control abstraction, Select.

```

DDD> (SingleLoop->Select sl)

(define select

(lambda (s p0 v0 v1 v2 v3)

(case s

[find (if p0 v0 v1)]

[wait (if p0 v2 v3)])))

```

(SingleLoop->StrEqns SingleLoop) → StrEqns

Takes a single loop specification and returns the architectural component StrEqns - a set of stream equations.

$(ItrSys->SeqSys\ ItrSys) \rightarrow [Select\ StrEqns]$

Takes an iterative system specification and returns a sequential system. The sequential system is also optimized to eliminate redundant inputs to *Select*.

At this stage in design, a sequential system consisting of a control specification, and an architectural component have been derived. Although this step in the derivation is mechanical, not every sequential system describes an implementable circuit. The identification of like terms may be necessary to reduce the complexity of the circuitry; signals may have to be merged in order to satisfy certain target constraints; abstract data types such as memories, stacks, alu's, or some subprocess may have to be factored from the description in order to construct a circuit defined over more concrete signals; and the partitioning of the design may be necessary to satisfy logical and/or physical aspects of the design. These decisions are made by the designer. DDD is a tool by which these decisions may be explored while preserving the integrity of the specification.

This section presents some of the algebra that has been implemented in DDD to manipulate sequential systems. The algebra is fairly simple, yet powerful, and manipulates design descriptions in a natural way. A set of transformations, identification, merge, generalization, and distribution, are defined. From this set, two transformations fundamental to factorization, general factorization, and signal factorization, are defined. A set of add hoc transformations to add, rename, extract, and remove stream equations are also defined. A transformation to optimize the sequential system is defined. A transformation to partially evaluate the control specification with respect to a stream equation is defined. A set of transformations to derive a state generator are defined.

## 5.1 Transformations

Identification is giving a name to an expression by adding a signal equation for it. Identification of like terms by a single equation has the effect of eliminating redundant circuitry. Identifying (inc X) with Z in

$$(X \Leftarrow (Select p X (inc X) (inc X)))$$

$(Y \Leftarrow (Select p Y (inc X) Y))$

returns

$$(X \Leftarrow (Select p X Z Z))$$

$(Y \Leftarrow (Select p Y Z Y))$

$(Z = (Select p ? (inc X) (inc X))$

Merge Equations is a merging of signal equations by instantiating don't cares, which are denoted by '?', and like terms. Merging allows multiple signals to share a common bus. Merging X and Y

$$(X = (Select p Z ? X))$$

$(Y = (Select p ? W X))$

returns

$$(XY = (Select p Z W XY))$$

Generalization is the introduction of don't care arguments to normalize function calls across Select. Generalizing

$$(X = (Select p (f x y) (g u v w))))$$

returns

$$(X = (Select p (f' x y ?) (g u v w)))$$

with f extended to

Distribution is the distribution of Select over function application. Distributing Select over add, and sub in

$$(X = (Select p (add W X) (sub Y Z)))$$

returns

$$(X = ((Select p add sub) (Select p W Y) (Select p X Z)))$$

### 5.2 Factorization

A system factorization encapsulates a subsystem in order to remove some collection of operations from the description. The encapsulated subsystem is called an *abstract component*. The transformation maintains the correct connectivity between the system description and the factored component. This technique of encapsulation yields a circuit defined over more concrete signals.

There are two ways of doing factorizations. The first, called a *general factorization*, is to state the set of operations that are to be encapsulated. The subject terms are those in which members of the set are applied. The second, called a *signal factorization*, encapsulates a signal; in this case the subject terms are those in which that signal's name occurs as an argument.

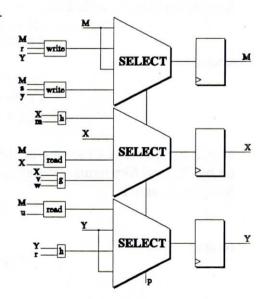

Consider the partial system description and its corre-

sponding circuit characterization:

$$(M \leftarrow (Select p M (write M r Y) M (write M s y))))$$

$$(X \leftarrow (Select p (h X m) X (read M X) (g X v w)))$$

$$(Y \Leftarrow (Select p (read M u) Y (h Y r) Y))$$

Algebra on Sequential Systems

## 5.2.1 General Factorization

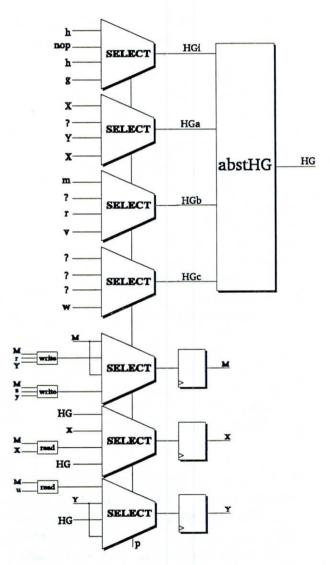

Applying a general factorization on operations h and g

```

(M \leftarrow (Select p \ M \ (write \ M \ r \ Y) \ M \ (write \ M \ s \ y))))

(X \leftarrow (Select p \ (h \ X \ m) \ X \ (read \ M \ X) \ (g \ X \ v \ w)))

(Y \leftarrow (Select p \ (read \ M \ u) \ Y \ (h \ Y \ r) \ Y))

```

yields

```

(HG = (abstHG HGi HGa HGb HGc))

(HGi = (Select p h nop h g))

(HGa = (Select p X ? Y X))

(HGb = (Select p m ? r v))

(HGc = (Select p ? ? ? w))

(M \leftarrow (Select p M (write M r Y))

M (write M s y)))

(X \leftarrow (Select p HG X (read M X) HG))

(Y \Leftarrow (Select p (read M u) Y HG Y))

where

(define abstHG

(lambda (i a b c)

(case i

(nop ?)

(h (h a b))

(g (g a b c)))))

```

The subject terms (g X v w), (h X m) found in X, and (h Y r) found in Y, are identified and replaced with the output of the subsystem, HG. The subject terms are collated, and a set of combinational signals: an instruction signal, HGi, and three inputs to the subsystem, HGa, HGb, and HGc, are synthesized. A functional specification of the factored subsystem, abstHG, and its application in the description, (abstHG HGi HGa HGb HGc) are also synthesized.

The factored component, **abstHG**, becomes a "black box" from the perspective of the system description. The operations **h** and **g** have been encapsulated and only residual signals necessary to communicate with the black box are maintained within the description. The factorization of **h** and **g** represents a design decision which removes these operations from the description. The effect on the system description is a set of stream equations defined over more concrete signals.

## 5.2.2 Signal Factorization

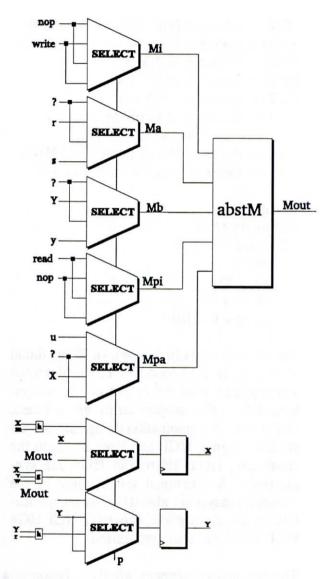

yields

Consider again the partial system description. Applying a signal factorization on M

```

(M \leftarrow (Select p M (write M r Y) M (write M s y))))

(X \leftarrow (Select p (h X m) X (read M X) (g X v w)))

(Y \leftarrow (Select p (read M u) Y (h Y r) Y))

```

```

(Mout = (abstM Mi Ma Mb Mpi Mpa))

(Mi = (Select p nop write nop write))

(Ma = (Select p ? r ? s))

(Mb = (Select p ? Y ? v))

(Mpi = (Select p read nop read nop))

(Mpa = (Select p u ? X ?))

(X \leftarrow (Select p (h X m) X Mout)

(g X v w)))

(Y \Leftarrow (Select p Mout Y (h Y r) Y))

where

(define abstM

(lambda (i a b c d)

(letrec

((M (Interpret(M i a b)))

(Interpret

(lambda (m i a b)

(case i

(nop m)

(write (write m a b))))))

(case c

(nop ?)

(read (read M d))))))

```

Each of the operations found in the defining equation for M, such as, (write M r Y), (write M s y), are called *constructors*, since they return a new M. Each of the operations on M that occur outside the defining equation, such as, (read M u), are called *probes*,