# Using the AMD 2901/2909 as a Dedicated Floating Point Adder

by

Jonathan W. Mills

Computer Science Department

Indiana University

Bloomington, IN 47405

TECHNICAL REPORT NO. 261

Using the AMD 2901/2909 as a

Dedicated Floating Point Adder

by

Jonathan W. Mills

September, 1988

# Using the AMD 2901 / 2909 as a Dedicated Floating Point Adder

#### Jonathan W. Mills

#### 1. Introduction

Typical solutions to the floating point adder problem assume that the microcode will be run on a homogeneous bit-slice machine: one where all slices execute the same microcode. This results in some long and involved microcode sequences that do not exploit the parallelism that is available to the user of bit-slice products.

In this solution I shall treat the AMD 2901 as a "piece of logic", and build a floating point adder that depends much more on the interconnection between chips, and upon microcode as "software wire-wrapping" rather than low level assembly language.

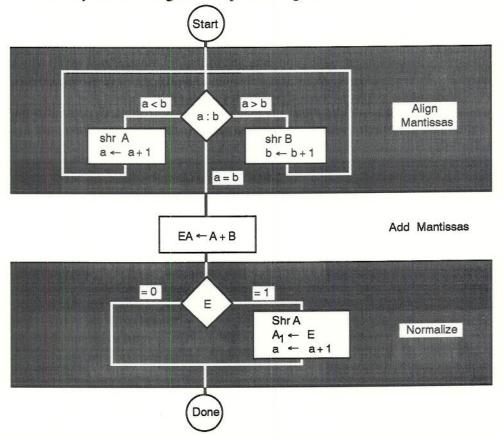

## 2. Simplification of the Algorithm

The first thing to do is to examine the problem statement, and compare it to the algorithm shown in Figure 10-8 of the handout. As it turns out, the restrictions simplify things considerably:

a. Only addition is to be performed,

b. Only 16-bit numbers are implemented, and

Addend and augend are greater than zero.

This leaves us with only the following relevant parts of Figure 10-8:

Looking at this algorithm it is apparent that the format of the floating point numbers used can be simplified, especially if we have only 16 bits to apportion. No sign bit is necessary — addend and augend are both > 0. If we allow the fact that a 2901 bit slice is 4 bits wide to influence us, then we can divide the number into a 4 bit exponent and a 12 bit mantissa. The exponent is expressed in excess-8 format to avoid manipulating an exponent sign bit, and allow easy comparisons over the entire exponent range.

## 3. Key Design Decisions

We will make a number of decisions that will influence the design. They are summarized below:

a. This is a dedicated piece of special-purpose hardware,

b. Some extra "glue" logic is acceptable,

c. The device operates correctly only under the conditions shown in paragraph (2),

d. Exponent and mantissa slices are not homogeneous,

e. Parallelism available from the hardware will be exploited.

Decisions (a), (b) and (c) allow us to wire the 2901 bit slices in an arbitrary, application specific way. There is no need to connect the slices to allow the full range of arithmetic and logical operations on general operands. Any "tricks" that we can play to obtain high performance (raw speed) will be acceptable. As will be seen later, we shall play some.

Probably the most interesting decisions are (d) and (e). As a consequence we shall microprogram the exponent slice using one control word, and the mantissa slices with a separate control word. This gives a wider, more horizontal control word, but one that we can still control with a single microprogram sequencer. This organization allows for fine-grained parallelism, and high speed operation.

The overall design of the floating point adder (FP adder) is shown below:

|                           | Exponent<br>Microprogram | Mantissa<br>Microprogram |

|---------------------------|--------------------------|--------------------------|

| Microprogram<br>Sequencer |                          |                          |

|                           | Exponent Slice           | Mantissa Slices          |

What the figure does <u>not</u> show are the interconnections between the devices. These will be described as we find a need for them in the following sections.

# 4. Implementing the Algorithm in Hardware

A parallel microprogram for heterogeneously microcoded exponent and mantissa bit slices will overlap processing between microinstructions. For example, after aligning the mantissas it would be efficient to detect the zero condition resulting from equal exponents, and use the flag to trigger adding the mantissas. Thus we could overlap, or "fold", the addition into the microprogram loop that aligns mantissas. To do this we must find some way of making one microinstruction do three different things — for both the exponent and the mantissa!

A "horizontal algorithm" corresponding to the simplified flowchart is shown below:

| Step | Expo                      | nent M icroprog         | gram                        | Mantissa M icroprogram         |                                |                        |  |  |  |  |  |

|------|---------------------------|-------------------------|-----------------------------|--------------------------------|--------------------------------|------------------------|--|--|--|--|--|

| 1    | Compare t                 | the exponents a         | and b.                      | Do nothing to the mantissas    |                                |                        |  |  |  |  |  |

| 2    |                           | If a > b then<br>b← b+1 | If a = b then<br>do nothing | If a < b then<br>shift A right | If a > b then<br>shift B right | If a = b then<br>A + B |  |  |  |  |  |

| 3    | if overflow<br>then a ← a | from A + B in s         | tep 2,                      |                                | om A + B in step               |                        |  |  |  |  |  |

Step 1 must select one of the three actions in step 2, and it must do so in both control words. This suggests that part of each control word's input will be derived from the signals generated by the exponent's 2901 bit slice. The arithmetic result flags are used to detect the conditions named in the microprogram; let's try to use them as control signals.

Let us choose R1 for a and A, and R0 for b and B (we'll see why this choice was made a little later). Now let's program step 1 for the exponent:

| Α  | B   1 <sub>210</sub>   1 <sub>534</sub>   R,S   R op S |                      | Operation                                                                                                                   | <sup>1</sup> 876 |       | Dest | Description                           |                              |  |  |

|----|--------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------|-------|------|---------------------------------------|------------------------------|--|--|

| 0  | 1                                                      | 1                    | 1                                                                                                                           | Prince of the    |       | 1    | Х                                     | exponent b - exponent a,     |  |  |

| R0 | R1                                                     | A, B                 | S-R                                                                                                                         | R1 - R0          | Z     | С    | OVF                                   | discard result but set flags |  |  |

| b  |                                                        | tie carry-in<br>high | a - b<br>a=b<br>a>b<br>a <b< td=""><td>1 0 0</td><td>0 0 1</td><td></td><td>carry out (C) selects value to adjust</td></b<> | 1 0 0            | 0 0 1 |      | carry out (C) selects value to adjust |                              |  |  |

### and the mantissa:

| A  | A B I <sub>210</sub> |      | 1 534<br>R op S      | Operation | 187 | 76 | Dest | Description                                  |  |  |

|----|----------------------|------|----------------------|-----------|-----|----|------|----------------------------------------------|--|--|

| 0  | 1                    | 3    | 1                    |           | 3   |    | В    | B ← B - 0                                    |  |  |

| R0 | R1                   | 0, B | S-R                  | R1 - 0    | Z   | С  | OVF  | effectively a "no-op" for mantissa           |  |  |

| В  | Α                    |      | tie carry-in<br>high |           |     |    |      | don't confuse 2901 A & B with mantissa A & B |  |  |

Programming step 2 will be very "tricky". For the exponent we will want to change two fields based on the status of the zero (Z) and carry-out (C) flags:

1. The B-bus will address either R0 or R1, and

2. The destination will either be the B-bus register, or nothing (result discarded).

For the mantissa we will want to condition four fields:

1. The B-bus will address either R0 or R1,

2. The ALU source pair will be either A,B or 0,B,

3. The result will either be right shifted 1 bit before being stored in the B-bus register, or it will be stored in the B-bus register without shifting, and

4. The function will either be A + B or B - 0.

Let's tentatively microcode step 2 for the exponent:

| Α  | A B 1 <sub>210</sub> 1 <sub>534</sub> R,S R op S |      | 210 534                     |                         | eration I <sub>876</sub> Des |   | Dest | Description                    |

|----|--------------------------------------------------|------|-----------------------------|-------------------------|------------------------------|---|------|--------------------------------|

| 0  | 0/1                                              | 3    | 0                           |                         | 0/2                          |   | X/B  | increment either exponent a or |

| R0 | R0<br>or<br>R1                                   | 0, B | R+S<br>tie carry-in<br>high | increment<br>(R0 or R1) | Z                            | С | OVF  | exponent b, or do nothing      |

### and the mantissa:

| Α  | B I <sub>210</sub> I <sub>534</sub> R,S R op S |                    |                                          |                                            | 18 | 76 | Dest            | Description                                                                                                                                |

|----|------------------------------------------------|--------------------|------------------------------------------|--------------------------------------------|----|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 0/1                                            | 1/3                | 0/1                                      |                                            | 3  | 4  | N               | shift right either mantissa A or B, or                                                                                                     |

| R1 | R0<br>or<br>R1                                 | A, B<br>or<br>0, B | R+S<br>or<br>S-R<br>tie carry-in<br>high | R0 + R1<br>or<br>shift right<br>(R0 or R1) | Z  | С  | OVF\ 0/1 if add | add mantissas (we will condition add<br>by Z = 1 so that we will always get R0<br>+ R1)<br>3 = B,<br>4 = result shifted right 1 bit into B |

Finally, let's microcode step 3. This step will normalize the mantissa if an overflow occurred when the mantissas were added. Thus, we will condition fields in this step based on the <u>mantissa's</u> overflow (which we take from the most significant mantissa carry-out).

For the exponent we will increment exponent a and write it back if the mantissa overflowed:

| Α       | B   1 <sub>210</sub>   1 <sub>534</sub>   R,S   R op S |         | Operation                   | <sup>1</sup> 876 |   | Dest    | Description |                                |  |

|---------|--------------------------------------------------------|---------|-----------------------------|------------------|---|---------|-------------|--------------------------------|--|

| 0       | 1                                                      | 3       | 0                           | 0                |   | 0/2 X/B |             | either increment exponent a or |  |

| R0<br>b | R0 R1                                                  | R1 0, B | R+S<br>tie carry-in<br>high | increment<br>R1  | Z | С       | OVF         | do nothing                     |  |

The mantissa will be shifted right once, inserting a one in the most significant bit if the mantissa addition overflowed:

| Α       | B   1 <sub>210</sub>   1 <sub>534</sub>   R,S   R op S |   |                               | Operation                          | ition I <sub>876</sub> |   | Dest | Description                                                                  |

|---------|--------------------------------------------------------|---|-------------------------------|------------------------------------|------------------------|---|------|------------------------------------------------------------------------------|

| 1       | 1                                                      | 3 | 1                             |                                    | 3/4                    |   | R    | either pass mantissa A or                                                    |

| R0<br>B | R1 0,                                                  |   | S - R<br>tie carry-in<br>high | R1 or<br>R1 shifted<br>right 1 bit | Z                      | С | OVF  | shift it right 1 bit  3 = B,  4 = result shifted right 1 bit then put into B |

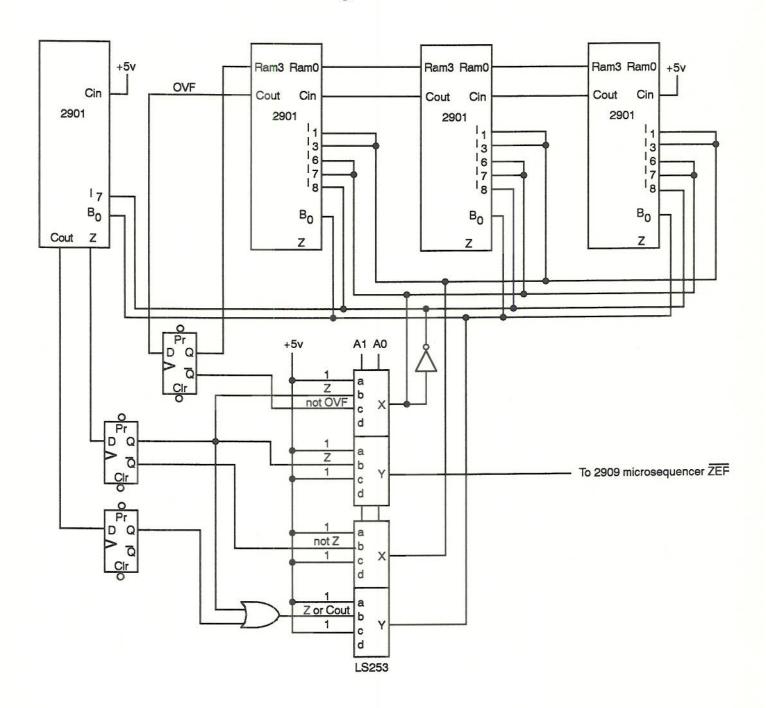

The next step — developing "glue" logic — took a couple of hours since an attempt was made to develop a boolean equation for all of the possibilities in the tentative microcode. The key observation here was that what we really want to do is sequence the inputs to certain I-bus and B-bus lines, thus generating the conditional microcode. This sequencing can be done trivially using a dual 1-of-4 multiplexer with selection done using microprogram address lines  $A_0$  and  $A_1$  (because we have only 3 microcode words we can even "splurge" with an extra multiplexer input and use it in the design). Such multiplexers (e.g., 74LS253) are cheap, costing about  $25\phi$ , and simple to wire. We will use two in the design.

Let's assume that the Z, C and OVF flags are not internally latched on the 2901, and become stable sometime during each microinstruction cycle. Let's also assume that the state of these flags is stable enough to be latched on the rising edge of each microinstruction clock pulse. We can latch the state of the flags for use in the next microinstruction with D flip-flops — even cheaper than multiplexers! — of which we'll need three. This translates into 2 74LS74's or something similar. We will need a few inverters and OR gates, but will assume that they are available as spares elsewhere in the design. All in all, we will use no more than 6 chips as "glue".

The circuit is shown on the next page. To be sure that the logic works, let's determine the microcode bits that the circuit generates, and see if they match those needed for the conditional microcode. The table below gives the 2901 and "glue" logic behavior:

| C    | Conditions Exponent |   |     |                |    | ent | Mantissa |    |    |                |      |                |     |                  |       |

|------|---------------------|---|-----|----------------|----|-----|----------|----|----|----------------|------|----------------|-----|------------------|-------|

| Addr | Z                   | С | OVF | B <sub>0</sub> | В  | 17  | Dest     | Во | В  | l <sub>1</sub> | Src  | l <sub>3</sub> | Fxn | l <sub>876</sub> | Dest  |

| 0    | x                   | x | х   | 1              | R1 | 0   | х        | 1  | R1 | 1              | 0, B | 1              | S-R | 3                | В     |

| 1    | 0                   | 0 | х   | 0              | RO | 1   | R0       | 0  | RO | 1              | 0, B | 1              | S-R | 4                | shr B |

| 1    | 0                   | 1 | х   | 1              | R1 | 1   | R1       | 1  | R1 | 1              | 0, B | 1              | S-R | 4                | shr B |

| 1    | 1                   | 0 | х   | 1              | R1 | 0   | х        | 1  | R1 | 0              | A, B | 0              | R+S | 3                | В     |

| 2    | x                   | x | 0   | 1              | R1 | 0   | x        | 1  | R1 | 1              | 0, B | 1              | S-R | 3                | В     |

| 2    | x                   | х | 1   | 1              | R1 | 1   | R1       | 1  | R1 | 1              | 0, B | 1              | S-R | 4                | shr B |

As can be seen from this table, the 2901 conditional microcode can be generated from the circuit given. Certain bits in each microinstruction are provided by feeding 2901 latched conditions from the previous microinstruction through the multiplexers. This means we need only three microinstructions for our floating point add.

Branching is taken care of by feeding either 1 or the zero flag (Z) into the 2909 microsequencer's NOT ZERO input, and using it to force a transfer back to address 0— the start of the addition— if the mantissas are not normalized. As soon as the mantissas are equal, and Z = 1, then the 2909 will allow the final microinstruction to execute. Note that we only need one 2909 slice!

Will this solution give us speed? Well, if we assume a random distribution of numbers to be added, then the mean number of alignment shifts will be approximately 4. Thus an average floating point add will take 9 microinstruction cycles. At worst, an add will take 23 cycles, and at best only three cycles will be needed. This is a substantial improvement over the more general solution, and shows how fast a dedicated processor may be. Remember, though, that this design is good for one and only one thing. If you need more flexibility, this is <u>not</u> the way to go ... but isn't it fun to design little hot-rods like this?

# Dedicated AMD 2901 Floating Point Adder